Tulang punggung sistem perangkat lunak yang handal terletak pada bagaimana kita memodelkan perilaku seiring waktu. Diagram state, yang sering disebut sebagai diagram mesin state, telah menjadi alat krusial bagi pengembang dan arsitek selama puluhan tahun. Mereka menyediakan representasi visual dari berbagai keadaan yang dapat diisi oleh suatu objek atau sistem serta transisi yang terjadi di antaranya. Seiring arsitektur perangkat lunak berpindah dari struktur monolitik ke ekosistem terdistribusi yang berbasis peristiwa, peran pemodelan state sedang mengalami transformasi signifikan.

Panduan ini meninjau lintasan evolusi diagram state, mengeksplorasi bagaimana konsep mesin state hingga batas tertentu beradaptasi terhadap tantangan kontemporer seperti konkurensi, skalabilitas, dan verifikasi otomatis. Kami akan menganalisis pergeseran dari pemodelan statis ke visualisasi dinamis saat runtime dan membahas implikasinya terhadap pemeliharaan sistem jangka panjang.

🏛️ Pondasi: Pemodelan State Klasik

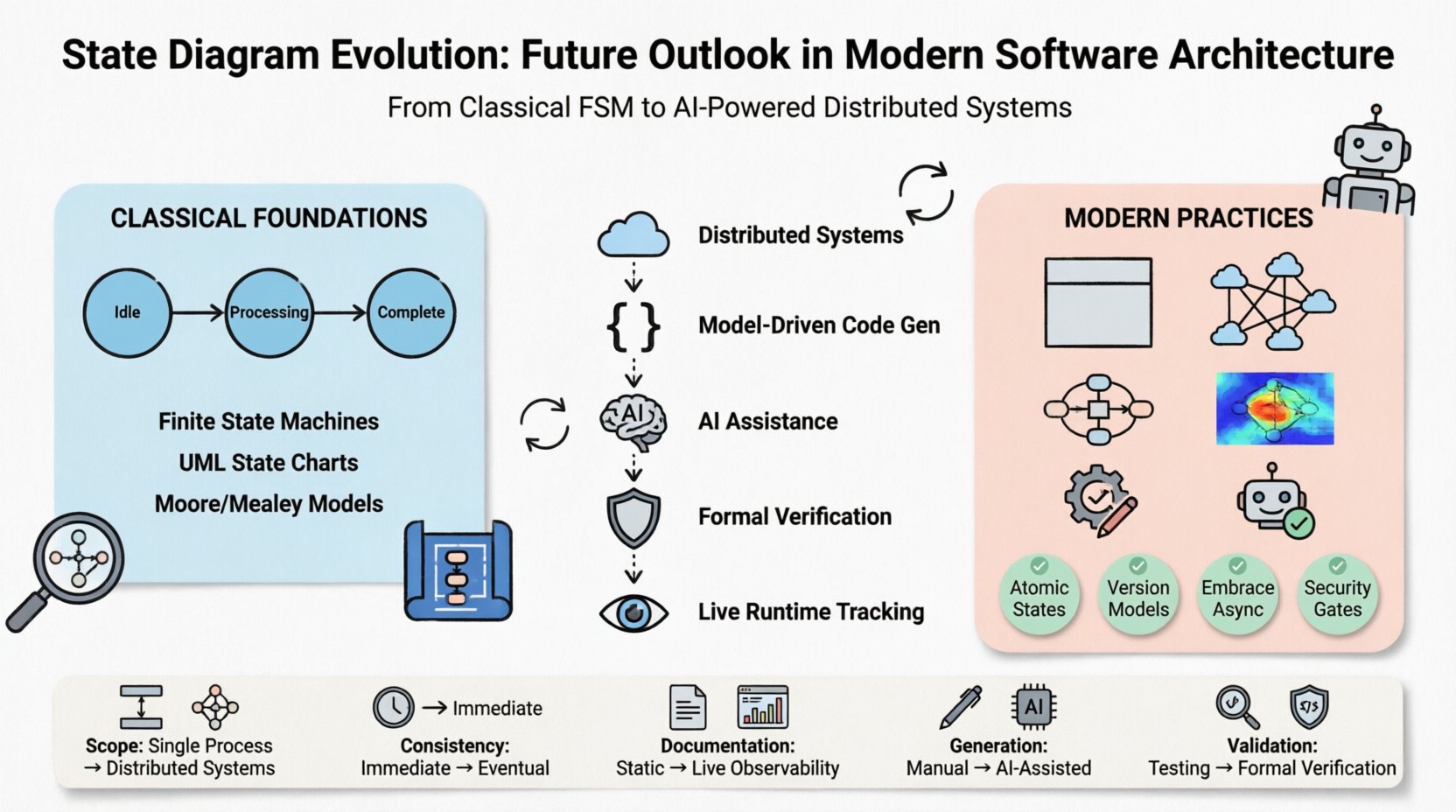

Sebelum masuk ke tren masa depan, sangat penting untuk memahami dasar-dasarnya. Diagram state klasik berakar pada logika formal dan teori otomata. Mereka mendefinisikan suatu sistem sebagai kumpulan keadaan, peristiwa, dan transisi. Pada masa awal rekayasa perangkat lunak, diagram ini terutama digunakan untuk menggambarkan perilaku proses berbasis satu thread atau logika perangkat keras.

- Mesin State Hingga (FSM): Sebuah model matematis komputasi di mana suatu sistem hanya dapat berada dalam satu keadaan pada satu waktu. Transisi terjadi berdasarkan input tertentu.

- Diagram Mesin State UML: Perluasan dari FSM yang memperkenalkan fitur seperti keadaan hierarkis, keadaan bersamaan (wilayah ortogonal), dan keadaan riwayat. Ini memungkinkan representasi logika yang lebih kompleks dalam satu diagram saja.

- Mesin Moore vs. Mesin Mealy: Perbedaan mendasar dalam cara output dihasilkan. Mesin Moore menghasilkan output berdasarkan keadaan saat ini, sedangkan mesin Mealy mengandalkan keadaan saat ini dan input.

Model dasar ini memberikan kejelasan. Namun, seiring sistem menjadi lebih kompleks, sifat statis dari diagram ini mulai menunjukkan keterbatasan ketika diterapkan pada lingkungan modern yang berbasis cloud.

☁️ Tantangan Terdistribusi: State dalam Microservices

Perpindahan menuju arsitektur microservices membawa perubahan paradigma. Dalam sistem monolitik, state sering disimpan di memori lokal atau basis data bersama. Dalam sistem terdistribusi, state terpecah di berbagai layanan. Fragmentasi ini mempersulit visualisasi dan pengelolaan transisi state.

🔗 Konsistensi Akhir dan State

Dalam lingkungan terdistribusi, konsistensi segera sering dipertukarkan demi ketersediaan dan toleransi terhadap pemisahan jaringan. Diagram state kini harus mempertimbangkan konsistensi akhir. Suatu transisi yang dahulu bersifat atomik kini dapat meluas ke beberapa layanan seiring waktu.

- Kompleksitas Temporal:Transisi tidak lagi instan. Penundaan, ulangan, dan kegagalan parsial harus dimodelkan.

- Transaksi Kompensasi:Jika transisi state gagal di tengah jalan, sistem membutuhkan jalur yang didefinisikan untuk kembali. Ini memperkenalkan ‘keadaan kompensasi’ yang jarang dibutuhkan dalam desain monolitik.

- Koreografi vs. Orkestrasi:Manajemen state bisa terdesentralisasi (koreografi) atau terpusat (orkestrasi). Diagram harus mencerminkan siapa yang mengendalikan aliran perubahan state.

📊 Membandingkan Pendekatan Manajemen State

| Fitur | Monolit Tradisional | Sistem Terdistribusi Modern |

|---|---|---|

| Lokasi State | Memori Lokal / DB Bersama | Cache Terdistribusi / Log Peristiwa |

| Latensi Transisi | Nanodetik | Milidetik ke Detik |

| Penanganan Kegagalan | Rollback / Pengecualian | Coba Lagi / Saga / Kompensasi |

| Visibilitas | Satu Thread | Banyak Aliran Konkuren |

| Cakupan Diagram | Satu Komponen | Alur Kerja Seluruh Sistem |

🧩 Teknik Rekayasa Berbasis Model dan Generasi Kode

Salah satu evolusi paling signifikan dalam penggunaan diagram status adalah perpindahan menuju Teknik Rekayasa Berbasis Model (MDE). Alih-alih menulis kode dan kemudian mendokumentasikannya dengan diagram, para pengembang mulai mendefinisikan diagram terlebih dahulu dan menghasilkan kode implementasi secara otomatis.

Pendekatan ini menawarkan beberapa keunggulan:

- Sumber Kebenaran Satu-Satunya: Diagram menjadi spesifikasi. Kode diperoleh dari diagram tersebut, mengurangi risiko penyimpangan dokumentasi.

- Validasi pada Waktu Desain: Kesalahan logika dapat terdeteksi sebelum kompilasi. Kebuntuan dan status yang tidak dapat dicapai dapat diidentifikasi selama fase pemodelan.

- Netral Bahasa Pemrograman: Model mesin status yang sama dapat dikompilasi ke dalam bahasa pemrograman yang berbeda, memfasilitasi persistensi poliglot dan pengembangan mikroservis.

Namun, ini membutuhkan alat yang kuat. Lapisan abstraksi harus akurat. Jika kode yang dihasilkan terlalu panjang atau tidak efisien, manfaat dari pemodelan akan berkurang. Fokus beralih ke model berkepadatan tinggi yang dapat dipetakan secara bersih ke konteks eksekusi saat runtime.

🤖 Kecerdasan Buatan dan Otomasi dalam Pemodelan Status

Integrasi kecerdasan buatan ke dalam proses pengembangan perangkat lunak memengaruhi bagaimana diagram status dibuat dan dipelihara. Model Bahasa Besar (LLM) semakin mampu memahami persyaratan bahasa alami dan mengubahnya menjadi definisi mesin status yang terstruktur.

🔍 Generasi Diagram Otomatis

Pengembang dapat memasukkan sekelompok cerita pengguna atau persyaratan fungsional. Kecerdasan buatan menganalisis teks untuk mengidentifikasi status dan transisi yang mungkin. Ini tidak menggantikan pengawasan manusia tetapi mempercepat tahap penyusunan awal.

- Pengenalan Pola: Kecerdasan buatan dapat menyarankan pola standar, seperti putaran ulang atau status waktu habis, berdasarkan data historis.

- Penyempurnaan: Kecerdasan buatan dapat membantu merefaktor diagram yang kompleks, memecah status monolitik menjadi sub-status yang lebih kecil dan mudah dikelola.

- Terjemahan Kode Mengonversi diagram visual menjadi kode boilerplate untuk lingkungan runtime tertentu.

🧠 Analisis Prediktif

Sistem masa depan dapat menggunakan AI untuk memprediksi transisi status berdasarkan pola penggunaan. Jika sistem mendeteksi kemungkinan tinggi suatu urutan status tertentu, maka sistem dapat mengambil sumber daya terlebih dahulu atau mengoptimalkan jalur transisi. Ini menggeser manajemen status dari reaktif menjadi proaktif.

🛡️ Verifikasi dan Metode Formal

Dalam sistem kritis—seperti kesehatan, keuangan, atau kontrol otonom—biaya kesalahan status terlalu tinggi untuk hanya mengandalkan pengujian. Verifikasi formal memastikan bahwa diagram status memenuhi sifat matematis tertentu.

- Analisis Keterjangkauan:Memastikan setiap status dapat dicapai dari status awal tanpa melanggar batasan.

- Deteksi Kebuntuan:Membuktikan secara matematis bahwa sistem tidak dapat memasuki status di mana tidak ada transisi yang mungkin.

- Pemeriksaan Invarian:Memverifikasi bahwa kondisi tertentu (invarian) tetap benar terlepas dari status saat ini.

Seiring perkembangan alat, verifikasi formal menjadi lebih mudah diakses oleh tim rekayasa perangkat lunak umum, bukan hanya mereka di industri yang kritis terhadap keselamatan. Tren ini mendorong diagram status menjadi lebih ketat, memperlakukan mereka sebagai spesifikasi yang harus dibuktikan kebenarannya, bukan sekadar dokumentasi.

🎨 Debugging Visual dan Observabilitas Runtime

Ada kesenjangan signifikan antara diagram desain statis dan perilaku dinamis saat runtime. Alat diagram status masa depan sedang menutup kesenjangan ini melalui observabilitas langsung.

📡 Pelacakan Status Langsung

Sistem pemantauan modern dapat menampilkan jalur eksekusi aktual sistem di atas diagram status asli. Ini memungkinkan arsitek melihat jalur mana yang benar-benar digunakan dalam produksi.

- Peta Panas:Memvisualisasikan frekuensi transisi. Status yang jarang digunakan dapat diidentifikasi untuk dihapus.

- Deteksi Anomali:Menyoroti transisi yang terjadi di luar model yang diharapkan. Ini sangat penting untuk audit keamanan dan mendeteksi bug logika.

- Korelasi Waktu:Menghubungkan transisi status dengan log atau metrik tertentu untuk memahami bottleneck kinerja.

🔒 Implikasi Keamanan dari Manajemen Status

Diagram status bukan hanya tentang alur logika; mereka tentang batas keamanan. Manajemen status yang tidak tepat merupakan penyebab utama kerentanan, seperti referensi objek langsung yang tidak aman atau kontrol akses yang rusak.

🚧 Kontrol Akses Berbasis Status

Izin sebaiknya sering dikaitkan dengan status sistem. Misalnya, dokumen dalam status “Draf” dapat diedit oleh penulis, tetapi begitu berpindah ke status “Diterbitkan,” hanya admin yang dapat mengubahnya. Diagram status membantu memvisualisasikan gerbang izin ini.

- Serangan Transisi Status:Penyerang mungkin berusaha memaksa transisi ke status yang berhak tanpa menyelesaikan langkah-langkah antara. Diagram membantu mengidentifikasi celah-celah ini.

- Manajemen Sesi:Diagram status mendefinisikan siklus hidup sesi pengguna, termasuk login, timeout idle, dan logout. Pemodelan yang jelas mencegah kerentanan fiksasi sesi.

- Jejak Audit:Setiap transisi status seharusnya dicatat secara ideal. Diagram ini mendefinisikan peristiwa yang memicu pencatatan log tersebut.

🚀 Standar dan Protokol yang Muncul

Ekosistem di sekitar pemodelan status sedang berkembang. Standar baru muncul untuk memfasilitasi interoperabilitas antara alat pemodelan yang berbeda dan mesin runtime.

- Definisi Status Berbasis JSON:Berpindah dari format biner milik pihak tertentu ke standar berbasis teks seperti JSON atau YAML memungkinkan kontrol versi yang lebih baik dan kolaborasi yang lebih efektif.

- WebAssembly (WASM):Seiring meningkatnya popularitas WASM, mesin status dapat dikompilasi untuk berjalan secara efisien di browser atau lingkungan tanpa server, memungkinkan perilaku yang konsisten di berbagai platform.

- Subskripsi GraphQL:Perubahan status dapat dikirim secara real-time ke klien melalui subskripsi. Diagram status mendefinisikan peristiwa yang memicu subskripsi ini.

🧭 Praktik Terbaik untuk Membuat Model Status yang Tahan Masa Depan

Untuk tetap efektif seiring perkembangan arsitektur, praktik pemodelan status harus beradaptasi. Berikut adalah prinsip-prinsip utama untuk menjaga diagram status yang kuat dalam konteks modern.

1. Pertahankan Status yang Atomik

Hindari membuat status yang mewakili terlalu banyak kompleksitas. Jika suatu status melibatkan beberapa proses bersamaan, bagi menjadi wilayah-wilayah ortogonal. Ini meningkatkan keterbacaan dan kemudahan debugging.

2. Tentukan Tindakan Masuk dan Keluar yang Jelas

Pastikan setiap transisi memiliki logika masuk dan keluar yang didefinisikan. Ketidakjelasan di sini menyebabkan kondisi persaingan dalam implementasi. Gunakan kondisi penjaga untuk mencegah transisi yang tidak valid.

3. Versikan Model Anda

Sama seperti kode, diagram status harus diberi versi. Perubahan dalam logika bisnis harus menghasilkan versi baru dari model, memungkinkan kompatibilitas mundur selama penyebaran.

4. Pisahkan Kepentingan

Jangan mencampur logika status dengan logika persistensi data. Diagram harus menggambarkan perilaku, bukan penyimpanan. Pemisahan ini memungkinkan lapisan data di bawahnya berubah tanpa mengubah model kontrol alur.

5. Terima Asinkronitas

Desain diagram yang mengasumsikan adanya penundaan. Panggilan jaringan, penulisan ke basis data, dan masukan pengguna tidak instan. Model status ‘menunggu’ secara eksplisit alih-alih mengasumsikan penyelesaian segera.

📈 Jalan Masa Depan

Perkembangan diagram status bukan tentang menggantikannya, melainkan melengkapinya. Logika inti mesin status tetap valid, tetapi alat-alat di sekitarnya menjadi semakin kuat.

Kita sedang bergerak menuju masa depan di mana:

- Desain dan implementasi terhubung erat melalui generasi kode.

- Observabilitas saat runtime memberikan umpan balik ke model desain untuk perbaikan berkelanjutan.

- Verifikasi formal menjamin kebenaran dalam lingkungan dengan risiko tinggi.

- AI membantu dalam menghasilkan dan memvalidasi kompleksitas alur kerja terdistribusi.

Arsitek yang memahami nuansa perkembangan status akan lebih siap membangun sistem yang tangguh, mudah dipelihara, dan aman. Diagram status tetap menjadi artefak penting, tetapi perannya telah berkembang dari gambaran statis menjadi komponen dinamis dalam siklus hidup perangkat lunak.

🧪 Pengujian Logika Mesin Status

Pengujian mesin status memerlukan pendekatan yang berbeda dibandingkan pengujian unit standar. Anda harus memverifikasi tidak hanya output dari suatu fungsi, tetapi juga status hasil dan validitas transisi yang terjadi.

- Cakupan Status:Pastikan setiap status dicapai selama pengujian.

- Cakupan Transisi:Verifikasi bahwa setiap panah pada diagram dilalui.

- Kondisi Batas:Uji transisi yang terjadi di tepi validitas (misalnya, jumlah maksimal percobaan ulang).

- Eksekusi Secara Bersamaan:Uji skenario di mana beberapa peristiwa tiba secara bersamaan untuk memastikan mesin menangani kondisi persaingan dengan benar.

Rangkaian pengujian otomatis untuk mesin status semakin umum digunakan. Alat-alat ini memungkinkan pengembang menentukan urutan peristiwa dan menegaskan status akhir, sehingga pengujian regresi untuk logika kompleks menjadi memungkinkan.

📝 Ringkasan Perubahan Utama

Untuk merangkum perubahan besar yang dibahas, pertimbangkan ringkasan berikut mengenai evolusi dari masa lalu ke masa depan.

| Aspek | Fokus Masa Lalu | Fokus Masa Depan |

|---|---|---|

| Cakupan | Proses Tunggal | Sistem Terdistribusi |

| Konsistensi | Segera | Akhirnya / Kausal |

| Dokumentasi | Diagram Statis | Observabilitas Langsung |

| Generasi | Pengkodean Manual | Dorong Model / Kecerdasan Buatan |

| Validasi | Pengujian Manual | Verifikasi Formal |

Dengan mengakui pergeseran-pergeseran ini, tim teknik dapat lebih baik mempersiapkan strategi arsitektur mereka. Diagram keadaan tidak lagi sekadar gambar; ia adalah kontrak antara niat desain dan kenyataan saat runtime. Seiring perangkat lunak terus menjadi lebih kompleks, disiplin dalam memodelkan keadaan secara akurat menjadi keunggulan kompetitif.

Menginvestasikan waktu untuk menyempurnakan praktik pemodelan keadaan hari ini akan memberi keuntungan dalam stabilitas sistem di masa depan. Alat-alat semakin matang, teori-teorinya kokoh, dan kebutuhan akan spesifikasi perilaku yang jelas lebih besar dari sebelumnya.

🔍 Pikiran Akhir tentang Arsitektur

Perjalanan diagram keadaan dari bagan logika sederhana ke model terdistribusi yang kompleks mencerminkan perjalanan yang lebih luas dari rekayasa perangkat lunak itu sendiri. Kita telah berpindah dari komponen yang terisolasi ke ekosistem yang saling terhubung. Melalui transisi ini, kebutuhan akan kejelasan tidak berkurang; justru semakin meningkat.

Pengembang dan arsitek yang mengutamakan pemodelan keadaan akan menemukan diri mereka lebih siap menghadapi kompleksitas infrastruktur modern. Baik menangani fungsi tanpa server, mikroservis yang dikontainerisasi, atau node komputasi tepi, prinsip-prinsip manajemen keadaan tetap konstan. Perbedaannya terletak pada lingkungan eksekusi dan alat-alat yang digunakan untuk memvisualisasikannya.

Saat kita melihat ke depan, integrasi model-model ini dengan kecerdasan operasional akan menentukan generasi berikutnya dari sistem perangkat lunak yang handal. Diagram keadaan tetap menjadi peta, tetapi kini merupakan peta hidup yang terus diperbarui oleh medan yang dilaluinya.