Mendesain mesin status yang kuat merupakan salah satu tugas paling kritis dalam arsitektur sistem. Ketika diimplementasikan dengan benar, diagram status memberikan kejelasan, prediktabilitas, dan kemudahan pemeliharaan. Namun, ketika logika bermasalah, sistem dapat memasuki keadaan di mana tidak ada kemajuan lebih lanjut yang mungkin terjadi. Keadaan ini dikenal sebagai kebuntuan. Dalam diagram mesin status, kebuntuan terjadi ketika sistem mencapai suatu status dari mana tidak ada transisi valid yang ada, menghentikan eksekusi secara tak terbatas. ⏸️

Panduan ini mengeksplorasi mekanisme desain mesin status, dengan fokus khusus pada mengidentifikasi dan mencegah kebuntuan. Kami akan membahas penjaga transisi, tindakan masuk dan keluar, wilayah konkuren, serta strategi validasi. Dengan mengikuti pendekatan terstruktur ini, Anda dapat memastikan diagram status Anda tetap tangguh dalam berbagai kondisi. 🔒

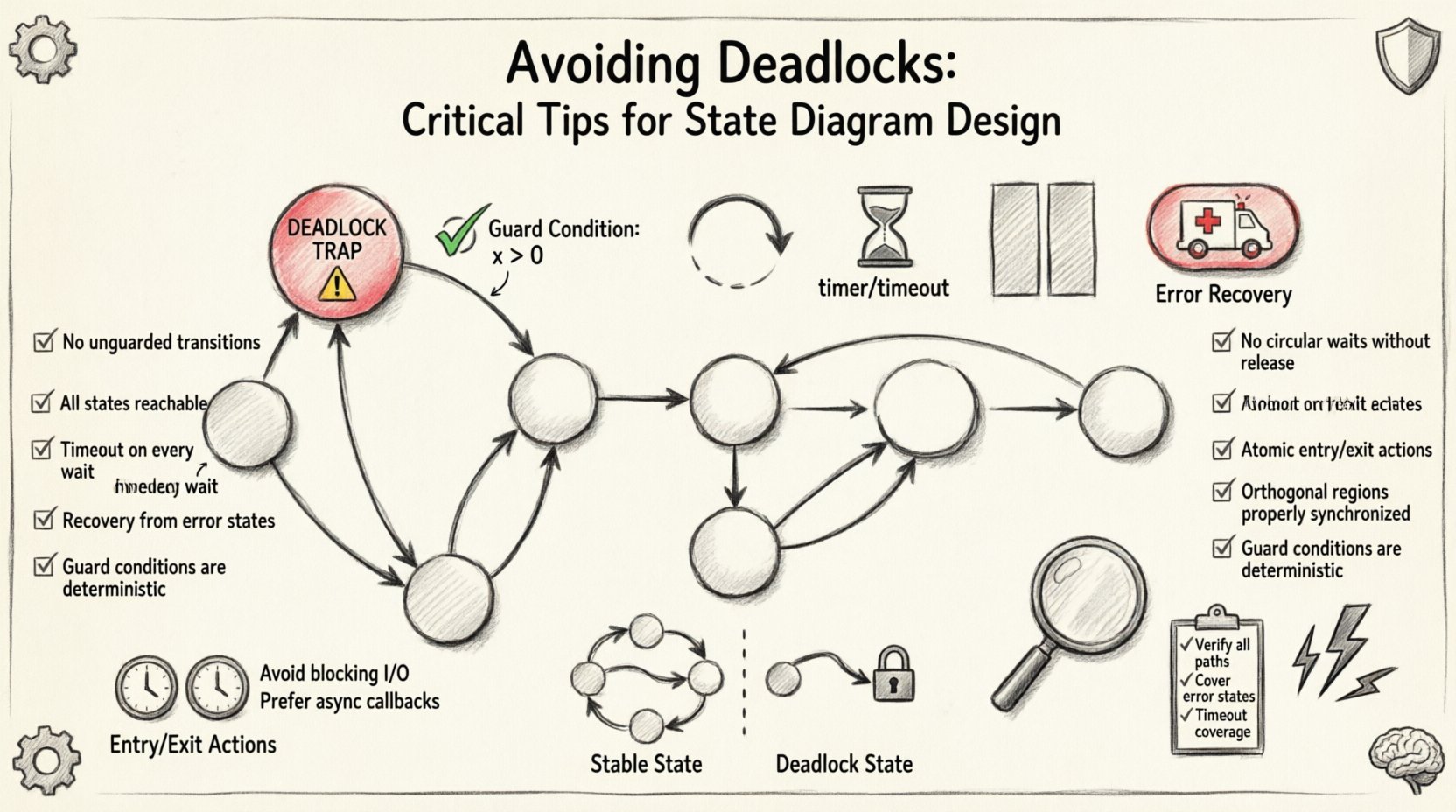

🧠 Memahami Kebuntuan Mesin Status

Kebuntuan dalam mesin status hingga (FSM) mewakili henti logis. Berbeda dengan kesalahan runtime yang bisa membuat aplikasi runtuh, kebuntuan sering mengakibatkan sistem tampak membeku meskipun masih berjalan. Mesin aktif, tetapi tidak dapat mengeksekusi perintah apa pun karena status saat ini tidak memiliki transisi keluar yang memenuhi kondisi pemicu. 🔍

Untuk mendesain secara efektif, seseorang harus memahami anatomi skenario kebuntuan. Ini jarang disebabkan oleh satu baris kode yang hilang. Sebaliknya, sering kali merupakan hasil dari interaksi kompleks antara beberapa status, penjaga, dan peristiwa eksternal. Berikut adalah ciri-ciri utama dari status kebuntuan:

- Tidak Ada Transisi Keluar: Status tersebut tidak memiliki panah yang keluar dari dalamnya.

- Transisi yang Tidak Dapat Dicapai: Semua panah keluar memiliki kondisi penjaga yang tidak pernah benar berdasarkan data saat ini.

- Jalur Default yang Hilang: Tidak ada transisi cadangan untuk menangani input yang tidak terduga.

- Pemegang Sumber Daya: Sistem memegang sumber daya (seperti kunci atau koneksi) tetapi menunggu kondisi lain yang tidak akan pernah terjadi.

Mencegah skenario-skenario ini membutuhkan filosofi desain proaktif, bukan debugging reaktif. Mari kita teliti akar penyebabnya secara rinci. 📉

⚠️ Penyebab Umum Kebuntuan dalam Desain Status

Kebuntuan bukan kecelakaan acak; mereka adalah hasil yang dapat diprediksi dari pilihan desain tertentu. Memahami pola-pola ini membantu Anda menghindarinya sebelum memengaruhi produksi. Berikut adalah penyebab utama terhentinya mesin status.

1. Penjaga Transisi yang Hilang

Ketika mendesain transisi, setiap panah yang keluar dari suatu status mewakili jalur maju yang mungkin. Jika suatu status memiliki beberapa input (peristiwa) yang mungkin, tetapi hanya beberapa yang dipetakan ke transisi, sistem akan berhenti ketika terjadi peristiwa yang tidak dipetakan. Ini sering disebut sebagai status ‘perangkap’. ❌

- Masalahnya: Mesin status mengharapkan pemicu tertentu. Jika pemicu yang tidak diharapkan datang, dan tidak ada transisi yang menanganinya, sistem akan tetap berada di tempatnya.

- Solusinya: Pastikan setiap status mempertimbangkan semua peristiwa yang didefinisikan, atau implementasikan handler default global untuk menangkap input yang tidak terduga.

2. Kondisi Penjaga yang Bertentangan

Kondisi penjaga adalah ekspresi boolean yang harus bernilai benar agar transisi dapat dipicu. Kesalahan umum terjadi ketika dua transisi berbagi status sumber dan peristiwa yang sama, tetapi kondisi penjaga mereka saling eksklusif atau tidak mencakup skenario yang mungkin. 🧩

- Masalahnya: Anda mendefinisikan transisi A (jika skor > 10) dan transisi B (jika skor < 5). Apa yang terjadi jika skor tepat 10? Jika logika ketat, keduanya mungkin gagal.

- Solusinya: Tinjau kondisi penjaga untuk kasus batas. Pastikan gabungan semua kondisi penjaga untuk peristiwa tertentu mencakup seluruh domain input.

3. Ketergantungan Melingkar

Dalam sistem yang kompleks, status dapat bergantung pada status status lain atau proses eksternal. Jika Status A menunggu Status B selesai, dan Status B menunggu Status A mengonfirmasi, maka keduanya tidak bergerak. Ini adalah kematian deadlock sinkronisasi klasik. ⏳

- Masalahnya:Logika terjalin sedemikian rupa sehingga memerlukan pengakuan timbal balik sebelum kemajuan terjadi.

- Perbaikannya:Putuskan siklus dengan memperkenalkan waktu habis (timeout) atau memungkinkan satu proses melanjutkan tanpa konfirmasi segera dari proses lain.

4. Penanganan Status Sejarah yang Tidak Tepat

Status sejarah memungkinkan sistem untuk mengingat status sebelumnya saat kembali masuk. Jika tidak diimplementasikan dengan benar, status sejarah dapat mengarah ke status yang tidak lagi valid atau telah dihapus. 🔄

- Masalahnya:Mesin berusaha beralih ke status sejarah yang tidak lagi ada atau tidak dapat diakses.

- Perbaikannya:Validasi bahwa target sejarah masih aktif saat mesin dihidupkan kembali atau diatur ulang.

🛡️ Pola Desain untuk Mencegah Kemacetan

Setelah Anda memahami risikonya, Anda dapat menerapkan pola-pola tertentu untuk mengurangi dampaknya. Pola-pola ini tidak spesifik perangkat lunak; berlaku untuk bahasa pemodelan apa pun atau kerangka implementasi.

1. Pola Status Default

Setiap mesin status harus memiliki titik masuk yang didefinisikan. Ini biasanya adalah status awal. Namun, di luar status awal, setiap status lainnya seharusnya memiliki jalur default. Jika suatu peristiwa tidak sesuai dengan kondisi tertentu, sistem harus kembali ke perilaku default yang aman. 📍

- Implementasi:Buat transisi ‘penangkap semua’ untuk setiap status yang menangani peristiwa yang tidak diketahui secara halus.

- Manfaat:Mencegah sistem memasuki status yang tidak terdefinisi saat terjadi input yang tidak terduga.

2. Pola Pengaman Waktu Habis

Kadang-kadang suatu status harus menunggu peristiwa eksternal yang mungkin tidak pernah datang. Untuk mencegah penungguan tak terbatas, Anda dapat memperkenalkan timer. Jika peristiwa tidak datang dalam durasi yang ditentukan, transisi waktu habis akan aktif. ⏱️

- Implementasi:Tambahkan transisi yang dipicu oleh peristiwa berbasis waktu (misalnya, “Timer Habis”.

- Manfaat:Memastikan sistem selalu bergerak maju, bahkan jika kondisi utama tidak terpenuhi.

3. Pola Status Paralel

Dalam alur kerja yang kompleks, satu status tidak dapat menangkap semua aktivitas bersamaan. Wilayah ortogonal memungkinkan Anda membagi suatu status menjadi beberapa sub-status independen. Ini mengurangi kompleksitas penjaga transisi. ⚡

- Implementasi:Gunakan status komposit dengan beberapa wilayah yang berjalan secara bersamaan.

- Manfaat:Mempermudah logika dengan memisahkan perhatian. Jika satu wilayah mengalami deadlock, wilayah lain masih dapat berfungsi atau melaporkan kesalahan.

4. Status Pemulihan Kesalahan

Rancang suatu status khusus yang didedikasikan untuk menangani kesalahan. Jika sistem mendeteksi anomali, ia akan langsung beralih ke status ini. Dari sini, sistem dapat mencoba melakukan reset, mencoba lagi, atau memberi peringatan kepada operator. 🚑

- Implementasi:Tambahkan status khusus ‘Kesalahan’ atau ‘Pemulihan’ yang dapat diakses dari berbagai titik.

- Manfaat:Mengisolasi kegagalan dan memberikan jalur yang jelas untuk pemulihan, bukan meninggalkan sistem dalam keadaan rusak.

📊 Perbandingan: Deadlock vs. Status Stabil

Untuk memvisualisasikan perbedaan antara keadaan sehat dan deadlock, pertimbangkan tabel perbandingan berikut. Ini menyoroti perbedaan struktural dalam desain.

| Fitur | Status Stabil | Status Deadlock |

|---|---|---|

| Transisi | Setidaknya satu transisi keluar yang valid ada. | Tidak ada transisi keluar yang memenuhi kondisi saat ini. |

| Logika Penjaga | Penjaga mencakup semua skenario input yang relevan. | Penjaga saling eksklusif atau tidak lengkap. |

| Penanganan Kejadian | Kejadian memicu tindakan yang diharapkan. | Kejadian diabaikan atau menyebabkan henti. |

| Pemulihan | Sistem memperbaiki diri sendiri atau melanjutkan ke fase berikutnya. | Sistem membutuhkan intervensi eksternal untuk memulai kembali. |

🧪 Strategi Validasi dan Pengujian

Desain hanyalah separuh pertarungan. Anda harus memvalidasi diagram untuk memastikan diagram tersebut tetap kuat di bawah tekanan. Pengujian mesin status membutuhkan pendekatan yang berbeda dibandingkan pengujian fungsi standar. 🧪

1. Pemeriksaan Model

Pemeriksaan model adalah metode verifikasi formal. Ini secara matematis membuktikan bahwa mesin status memenuhi sifat-sifat tertentu, seperti ‘tidak ada status yang dapat dicapai di mana deadlock terjadi’. Ini sangat efektif untuk sistem kritis. 🔢

- Teknik:Gunakan alat metode formal untuk menelusuri seluruh ruang status.

- Hasil:Jaminan matematis bahwa sistem tidak dapat memasuki keadaan deadlock.

2. Pengujian Cakupan Status

Pastikan setiap status dan setiap transisi diuji setidaknya sekali. Ini dikenal sebagai cakupan status. Jika suatu status tidak diuji, Anda tidak dapat mengetahui apakah status tersebut mengandung kondisi deadlock tersembunyi. 🎯

- Teknik:Tulis kasus uji yang memaksa sistem memasuki setiap status yang telah didefinisikan.

- Hasil:Verifikasi bahwa transisi berjalan dengan benar dari setiap titik masuk.

3. Pengujian Input Beban Berat

Kirim input yang tidak valid, null, atau tidak diharapkan ke sistem. Mesin status yang kuat seharusnya tidak macet atau terjebak saat diberi data buruk. Ia harus menolak input tersebut atau beralih ke status aman. 🌪️

- Teknik:Hasilkan input acak atau batas dan amati perilakunya.

- Hasil:Identifikasi kasus-kasus ekstrem yang menyebabkan deadlock.

4. Analisis Statis

Sebelum menjalankan kode, analisis struktur diagram. Cari status yang tidak memiliki panah keluar. Cari loop yang tidak pernah berakhir. Alat sering kali dapat mendeteksi pola-pola ini secara otomatis. 🔎

- Teknik:Jalankan skrip linting atau analisis statis pada file definisi status.

- Hasil:Deteksi dini kesalahan struktural.

🔄 Penanganan Konkurensi dan Status Paralel

Konkurensi menambah kompleksitas. Ketika beberapa wilayah beroperasi secara bersamaan, deadlock dapat muncul akibat masalah sinkronisasi. Anda harus memastikan bahwa jalur paralel tidak saling menghambat. 🏗️

1. Wilayah Mandiri

Pastikan status paralel benar-benar mandiri. Jika Status A di Wilayah 1 membutuhkan data dari Status B di Wilayah 2, Anda memperkenalkan ketergantungan. Ketergantungan ini dapat menjadi penghalang. 🚧

- Praktik Terbaik:Minimalkan pertukaran data antar wilayah ortogonal.

- Alternatif:Gunakan bus acara untuk berkomunikasi antar wilayah tanpa penghentian langsung.

2. Titik Sinkronisasi

Kadang-kadang status harus disinkronkan. Misalnya, Wilayah A harus selesai sebelum Wilayah B dimulai. Jika Anda menerapkannya secara manual, Anda berisiko mengalami deadlock. Gunakan konstruksi sinkronisasi bawaan yang disediakan oleh kerangka kerja Anda. ⚙️

- Praktik Terbaik: Hindari mekanisme penguncian manual kecuali benar-benar diperlukan.

- Alternatif: Gunakan status gabungan yang menunggu semua jalur masuk selesai secara alami.

⚙️ Tindakan Masuk dan Keluar

Tindakan masuk dan keluar adalah potongan kode yang berjalan saat memasuki atau meninggalkan suatu status. Ini merupakan sumber umum dari deadlock yang halus. ⚠️

1. Tindakan Masuk yang Menghambat

Jika tindakan masuk melakukan tugas berjalan lama (seperti permintaan jaringan) tanpa waktu habis, sistem tidak dapat meninggalkan status tersebut hingga tugas selesai. Jika tugas terjebak, mesin status akan terjebak. 🕸️

- Praktik Terbaik: Pertahankan tindakan masuk ringan dan tidak menghambat.

- Alternatif: Alihkan tugas berat ke pekerja latar belakang dan beralih ke status “Pemrosesan”.

2. Lingkaran Tak Hingga dalam Tindakan Keluar

Tindakan keluar seharusnya tidak pernah memicu transisi yang langsung kembali ke status yang sama. Ini menciptakan lingkaran yang menghabiskan sumber daya tanpa kemajuan. 🔄

- Praktik Terbaik: Pastikan tindakan keluar tidak memicu kembali transisi status yang sama.

- Alternatif: Gunakan bendera untuk mencegah pemicuan rekursif tindakan.

📝 Daftar Periksa Ulasan untuk Diagram Status

Sebelum menerapkan mesin status, lakukan daftar periksa ini. Ini mencakup area-area penting di mana deadlock biasanya tersembunyi. ✅

| Item Pemeriksaan | Lulus / Gagal | Catatan |

|---|---|---|

| Apakah semua status dapat diakses dari status awal? | ||

| Apakah setiap status memiliki setidaknya satu transisi keluar? | ||

| Apakah semua kondisi penjaga logis (tidak ada celah)? | ||

| Apakah ada mekanisme waktu habis untuk status yang menunggu? | ||

| Apakah wilayah paralel menghindari ketergantungan data langsung? | ||

| Apakah ada status pemulihan kesalahan global? | ||

| Apakah tindakan masuk telah diuji untuk perilaku yang menghambat? |

🔍 Penelitian Mendalam: Adegan Kasus Tepi

Bahkan dengan desain yang baik, kasus tepi bisa lolos. Berikut adalah skenario-spesifik di mana deadlock sering muncul di lingkungan produksi. 🌐

1. Jebakan Kondisi Persaingan

Ketika dua peristiwa terjadi secara bersamaan, urutan pemrosesan sangat penting. Jika mesin keadaan memproses Peristiwa A sebelum Peristiwa B, maka bisa mengambil jalur yang menyebabkan deadlock. Jika memproses B sebelum A, maka bisa berhasil. ⚡

- Penanggulangan:Antri peristiwa dan proses secara berurutan. Pastikan urutan peristiwa tidak memengaruhi validitas keadaan akhir.

2. Jebakan Kehabisan Sumber Daya

Suatu keadaan mungkin menunggu sumber daya (seperti koneksi basis data). Jika pool habis, tungguannya menjadi tak terbatas. Ini tampak seperti deadlock tetapi sebenarnya merupakan masalah sumber daya. 💾

- Penanggulangan:Terapkan waktu habis koneksi dan keadaan cadangan yang menurunkan fungsi secara halus.

3. Jebakan Perpindahan Konfigurasi

Diagram mungkin dirancang untuk Keadaan A, tetapi file konfigurasi menentukan Keadaan B. Jika logika transisi bergantung pada nilai konfigurasi yang hilang, sistem akan macet. 📄

- Penanggulangan:Validasi konfigurasi terhadap skema diagram keadaan saat startup.

🚀 Pertimbangan Akhir untuk Desain yang Kuat

Membangun mesin keadaan yang tahan terhadap deadlock adalah soal disiplin. Diperlukan antisipasi terhadap mode kegagalan dan merancang jalur menghindarinya. Dengan fokus pada transisi yang jelas, logika penjagaan yang komprehensif, dan penanganan kesalahan yang kuat, Anda menciptakan sistem yang tangguh terhadap perubahan. 🛡️

Ingat bahwa diagram keadaan adalah dokumen hidup. Seiring perubahan kebutuhan, diagram harus berkembang. Refactoring dan sesi tinjauan rutin memastikan fitur baru tidak membawa bug lama. Pertahankan model sederhana, pertahankan logika jelas, dan pertahankan jalur pemulihan yang terang. 🔄

Ketika Anda mengutamakan stabilitas daripada kecepatan pada tahap desain, Anda menghemat waktu signifikan dalam pemeliharaan nanti. Mesin keadaan yang dirancang dengan baik adalah tulang punggung perilaku perangkat lunak yang dapat diandalkan. Luangkan upaya dalam desain, dan sistem akan berjalan secara konsisten. 📈