Merancang sistem yang kompleks sering terasa seperti berjalan di labirin tanpa peta. Baik Anda sedang membangun alur otentikasi pengguna, kecerdasan buatan permainan, atau kontroler tertanam, logika bisa dengan cepat menjadi kusut. Sebuah diagram statusmemberikan kejelasan yang dibutuhkan untuk memvisualisasikan bagaimana suatu sistem berperilaku seiring waktu. Panduan ini menjelaskan cara membuat model Mesin State Hingga (FSM)menggunakan metode visual, menghilangkan notasi matematika yang rumit yang biasanya terkait dengan metode formal.

Pada akhir tutorial ini, Anda akan memahami komponen utama pemodelan status, cara menggambar transisi yang merepresentasikan logika dunia nyata, dan cara menghindari jebakan desain yang umum. Anda tidak perlu gelar dalam ilmu komputer untuk menggunakan alat-alat ini secara efektif. Anda hanya perlu pikiran yang jernih dan pendekatan yang terstruktur. Mari kita mulai.

🤔 Apa itu Mesin State Hingga?

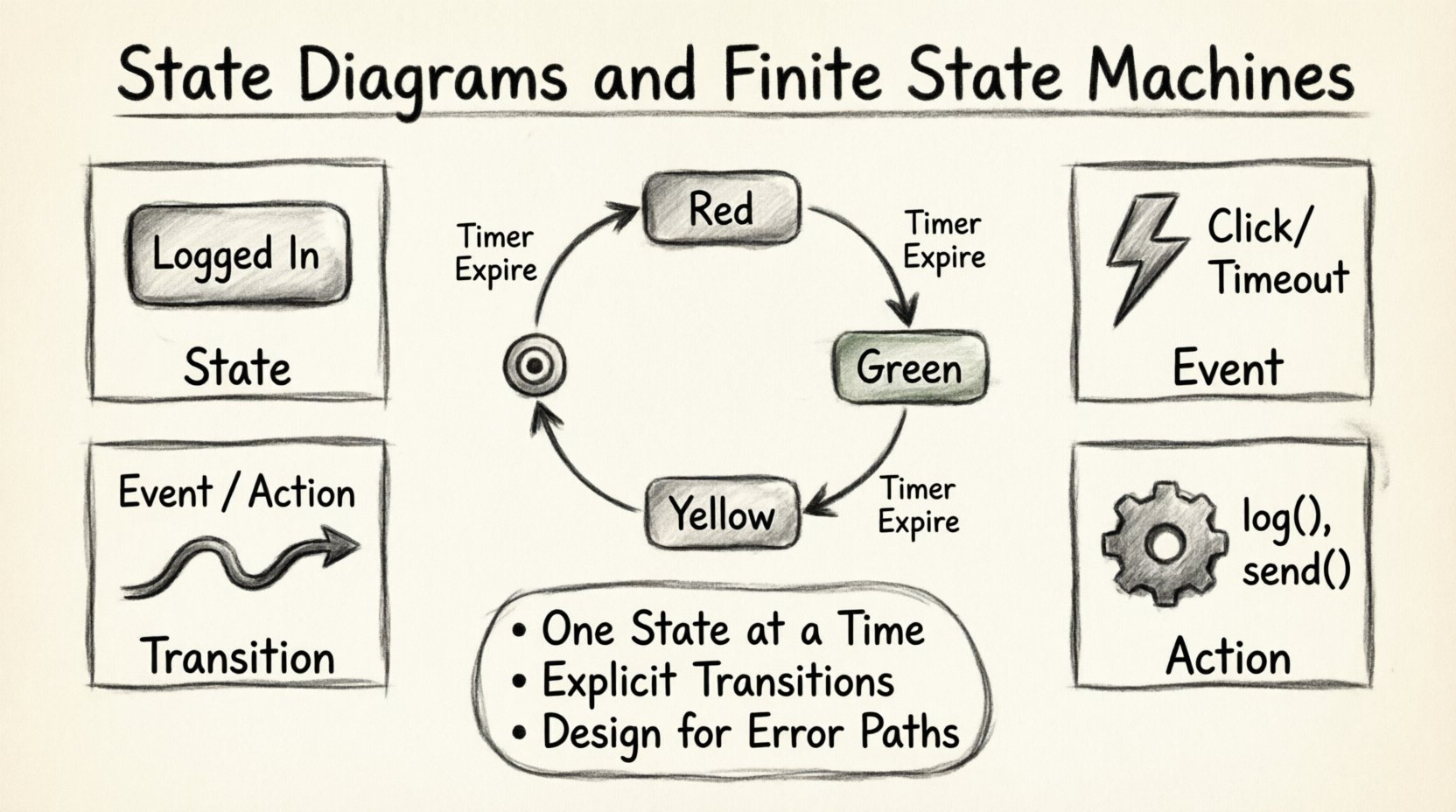

Mesin State Hingga adalah model matematis dari komputasi. Namun, memikirkan hal ini secara murni matematis menciptakan hambatan yang tidak perlu. Dalam rekayasa perangkat lunak dan sistem yang praktis, FSM hanyalah cara untuk menjelaskan bagaimana suatu objek mengubah perilakunya berdasarkan input. Ia memiliki jumlah terbatas statusyang dapat diisi pada setiap saat tertentu.

Pertimbangkan sakelar lampu sederhana. Ia memiliki dua status: Nyala dan Matikan. Ia bereaksi terhadap satu peristiwa: Balik Sakelar. Ini adalah FSM. Sekarang pertimbangkan mesin kopi. Ia memiliki status seperti Diam, Pemanasan, Penyeduhan, dan Kesalahan. Ia bereaksi terhadap peristiwa seperti Pilih Kopi, Air Rendah, atau Tombol Daya.

Poin utama adalah eksklusivitas. Pada setiap saat tertentu, sistem berada dalam tepat satu keadaan. Ia tidak dapat menjadi Pemanasan dan Pembuatan Kopi secara bersamaan kecuali Anda mendefinisikannya sebagai keadaan gabungan. Kesederhanaan ini adalah alasan mengapa diagram keadaan sangat kuat untuk dokumentasi dan debugging.

🛠️ Komponen Utama dari Diagram Keadaan

Untuk membuat diagram tanpa kebingungan, Anda harus memahami empat pilar pemodelan keadaan. Setiap diagram keadaan yang valid dibangun dari elemen-elemen ini.

- Keadaan: Ini mewakili kondisi sistem. Mereka adalah ‘kata benda’ dari logika Anda. Contohnya termasuk Masuk, Sedang Diproses, atau Menunggu.

- Kejadian: Ini adalah pemicu yang menyebabkan perubahan. Mereka adalah ‘kata kerja’ atau sinyal eksternal. Contohnya termasuk Klik, Waktu Habis, atau Data Diterima.

- Transisi: Ini adalah garis yang menghubungkan keadaan. Mereka menunjukkan jalur dari satu kondisi ke kondisi lain saat terjadi suatu kejadian.

- Aksi:Ini adalah tugas-tugas yang dilakukan selama transisi atau saat berada di dalam suatu keadaan. Ini adalah logika ‘apa yang terjadi selanjutnya’.

📊 Memahami Hubungan

| Komponen | Representasi Visual | Peran dalam Logika |

|---|---|---|

| Keadaan | Persegi Panjang Melengkung | Menyimpan konteks atau data saat ini. |

| Transisi | Panah dengan Label | Menentukan jalur dan pemicu. |

| Kejadian | Label Teks pada Panah | Secara khusus memicu perpindahan. |

| Aksi | Label Teks pada Panah | Menentukan efek samping (misalnya, log(), kirim()). |

🎨 Simbol dan Notasi Standar

Meskipun alat bantu bervariasi, notasi standar ada untuk memastikan diagram dapat dibaca oleh berbagai tim. Menggunakan simbol-simbol ini memastikan siapa pun yang membaca diagram Anda memahami maksudnya tanpa perlu legenda.

1. Keadaan Awal (Mulai)

Diagram dimulai di sini. Secara visual, ini adalah lingkaran hitam pejal. Ini mewakili titik masuk sistem. Ketika objek dibuat atau proses dimulai, ia langsung memasuki keadaan ini.

2. Keadaan Akhir (Akhir)

Diagram berakhir di sini. Secara visual, ini adalah lingkaran hitam pejal di dalam lingkaran yang lebih besar(bullseye). Ini mewakili penghentian proses. Suatu sistem dapat memiliki beberapa status akhir (misalnya, Sukses vs. Gagal).

3. Status Biasa

Ini adalah kondisi kerja. Mereka digambarkan sebagai persegi panjang melengkung. Nama status ditempatkan di dalamnya. Jika status memerlukan tindakan khusus yang terjadi saat menunggu, Anda dapat mencantumkannya di dalam kotak menggunakan notasi entry/ notasi.

4. Transisi

Garis dengan panah menunjukkan pergerakan. Harus selalu bergerak dari satu status ke status lain. Anda dapat kembali ke status yang sama jika logika mengharuskannya. Label pada garis biasanya mengikuti format:

Peristiwa: Pemicu./ Tindakan: Apa yang terjadi segera setelahnya.

Sebagai contoh: Kirim / Validasi berarti ketika peristiwa Kirim terjadi, sistem akan melakukan tindakan Validasi tindakan.

🚀 Panduan Pembuatan Model Langkah demi Langkah

Sekarang kita sudah tahu simbol-simbolnya, mari kita bahas proses membuat diagram dari awal. Ikuti langkah-langkah ini untuk memastikan konsistensi logis.

Langkah 1: Tentukan Lingkup

Sebelum menggambar, identifikasi batas-batas sistem. Apakah Anda memodelkan seluruh aplikasi, atau hanya modul login? Perluasan lingkup adalah musuh diagram yang jelas. Tentukan apa yang termasuk dalam dalam dan apa yang termasuk dalam keluar dari FSM.

Langkah 2: Daftar Semua Status yang Mungkin

Buat ide untuk setiap kondisi yang bisa ada dalam sistem. Tanyakan pada diri sendiri: ‘Apa yang bisa saya katakan tentang sistem ini sekarang?’

- Apakah sedang berjalan?

- Apakah sedang dijeda?

- Apakah sedang menunggu input?

- Apakah sedang dalam keadaan kesalahan?

Tuliskan hal-hal ini. Jangan khawatir tentang koneksi untuk saat ini. Hanya daftar kata benda.

Langkah 3: Identifikasi Peristiwa

Apa yang mengubah status? Daftar setiap masukan eksternal atau pemicu internal.

- Pengguna mengklik tombol.

- Waktu jaringan habis.

- Pertanyaan basis data dikembalikan.

- Waktu timer habis.

Langkah 4: Gambar Status Awal dan Akhir

Tempatkan lingkaran hitam di bagian atas (awal) dan lingkaran target di bagian bawah (akhir). Ini menjadi titik tetap diagram Anda.

Langkah 5: Hubungkan Status-Statusnya

Gambar panah antar status berdasarkan peristiwa Anda. Jika Status A bisa menjadi Status B ketika Peristiwa X terjadi, gambar garis dari A ke B dan beri label X. Pastikan tidak ada ujung yang terbuka kecuali sistem dirancang untuk macet (yang jarang terjadi).

Langkah 6: Tinjau untuk Menghindari Kebuntuan

Periksa setiap status. Apakah sistem bisa terjebak? Jika suatu status tidak memiliki panah keluar, maka itu adalah kebuntuan kecuali status tersebut adalah status akhir. Jika suatu status tidak memiliki panah masuk, maka tidak dapat diakses. Keduanya biasanya merupakan kesalahan dalam desain.

🌍 Contoh Dunia Nyata

Teori bersifat abstrak. Mari kita lihat skenario konkret untuk memperkuat konsep-konsep ini.

Contoh 1: Alur Masuk

Ini adalah pola umum dalam aplikasi web. Sistem berpindah berdasarkan input pengguna dan respons server.

- Status: Diam, Memvalidasi, Terverifikasi, Terblokir.

- Kejadian: Masukkan Kredensial, Respons Server, Jumlah Percobaan Maksimal.

- Logika:

- Dari Menganggur ke Memvalidasi pada Masukkan Kredensial.

- Dari Memvalidasi ke Terverifikasi pada Berhasil.

- Dari Memvalidasi ke Terblokir on Gagal (3 kali).

Logika ini mencegah pengguna menebak kata sandi tanpa batas dan menangani latensi jaringan dengan baik.

Contoh 2: Sistem Lampu Lalu Lintas

Sistem tertanam sangat bergantung pada FSM. Lampu lalu lintas harus berputar melalui warna-warna secara ketat.

- Status: Merah, Hijau, Kuning.

- Kejadian: Waktu Habis.

- Logika:

- Merah → (Waktu) → Hijau

- Hijau → (Waktu) → Kuning

- Kuning → (Waktu) → Merah

Perhatikan lingkaran tersebut. Dalam konteks ini, sistem tidak pernah mencapai ‘Status Akhir’; ini adalah proses yang berkelanjutan. Diagram ini mencerminkan siklus.

Contoh 3: Pemrosesan Pesanan E-Commerce

Logika bisnis yang kompleks membutuhkan manajemen status yang hati-hati untuk memastikan integritas data.

- Status: Baru, Lunas, Dikirim, Dikirim, Dibatalkan.

- Kejadian: Pembayaran Berhasil, Kirim Barang, Pelanggan Meminta Membatalkan.

- Kendala: Anda tidak dapat mengirim pesanan yang Dibatalkan. Diagram harus secara eksplisit mencegah transisi ini.

🧩 Konsep Lanjutan

Seiring sistem berkembang, alur linier sederhana menjadi tidak cukup. Anda mungkin perlu mengelola kompleksitas tanpa membuat diagram menjadi tidak dapat dibaca.

Substate (Hierarki)

Ketika suatu state berisi logika yang kompleks, Anda dapat menempatkan diagram lain di dalamnya. Ini disebut substate. Sebagai contoh, state Memutar pada pemutar media mungkin memiliki substate seperti Menyimpan Sementara, Dijeda, atau Mencari. Ini membuat diagram utama tetap bersih sambil menjelaskan perilaku internal dari suatu state tertentu.

Wilayah Ortogonal (Paralelisme)

Kadang-kadang suatu sistem melakukan beberapa hal sekaligus. Jika suatu state memiliki beberapa wilayah independen, itu berarti bagian-bagian tersebut beroperasi secara bersamaan. Sebagai contoh, jam tangan pintar mungkin sedang Melacak Detak Jantung dan Menyinkronkan Data pada saat yang sama. Diagram membagi kotak status menjadi bagian-bagian untuk menunjukkan aktivitas paralel ini.

Status Sejarah

Ketika pengguna keluar dari suatu status kompleks dan kembali, apakah sistem harus kembali ke awal status tersebut, atau melanjutkan dari titik di mana ia berhenti? Sebuah Status Sejarah (sering berupa lingkaran putus-putus) mengingat substatus aktif terakhir. Ini sangat penting untuk pengalaman pengguna dalam aplikasi mobile.

⚠️ Kesalahan Umum yang Harus Dihindari

Bahkan insinyur berpengalaman membuat kesalahan saat memodelkan. Waspadai jebakan umum ini.

- Status yang Tumpang Tindih: Jangan menggambar panah yang saling tumpang tindih. Gunakan routing atau garis melengkung untuk menjaga diagram tetap rapi. Garis yang saling tumpang tindih membingungkan pembaca.

- Penanganan Kesalahan yang Hilang: Setiap transisi harus mempertimbangkan apa yang terjadi jika terjadi kesalahan. Jika panggilan jaringan gagal selama Memvalidasi, ke mana panah itu pergi? Jika panah tidak pergi ke mana-mana, sistem akan gagal.

- Terlalu Banyak Status: Jika suatu status memiliki lebih dari 10 transisi masuk dan keluar, kemungkinan besar terlalu kompleks. Pisahkan menjadi substatus.

- Logika Implisit: Jangan mengasumsikan pembaca mengetahui aturan bisnisnya. Tulis peristiwa dan tindakan dengan jelas pada panah. Jangan biarkan penjelasan verbal saja.

- Mengabaikan Tindakan Masuk/Keluar: Kadang-kadang suatu tindakan terjadi segera setelah memasuki suatu status, bukan selama transisi. Gunakan

masuk/sintaks untuk membedakannya dari tindakan transisi.

🛡️ Praktik Terbaik untuk Pemeliharaan

Diagram status adalah dokumen hidup. Harus berkembang seiring perubahan perangkat lunak. Ikuti panduan ini agar dokumentasi Anda tetap bernilai.

- Jaga Tingkat yang Tinggi: Jangan peta setiap pemanggilan fungsi secara individual. Peta status logisnya saja. Detail implementasi teknis seharusnya ada di komentar kode, bukan di diagram.

- Gunakan Penamaan yang Konsisten: Jika Anda menyebut suatu status Memproses dalam satu diagram, jangan sebutkan Bekerjadalam yang lain. Konsistensi mengurangi beban kognitif.

- Validasi dengan Tim:Ulas diagram bersama pengembang dan manajer produk. Jika mereka menafsirkan suatu transisi berbeda dari yang Anda lakukan, maka diagram tersebut tidak jelas.

- Kontrol Versi:Perlakukan file diagram seperti kode. Lakukan komit perubahan saat logika berubah. Ini menciptakan jejak audit mengapa keputusan dibuat.

- Tautkan ke Kode: Jika memungkinkan, rujuk modul atau kelas tertentu yang menerapkan logika tersebut. Ini menghubungkan celah antara desain dan implementasi.

📈 Mengapa Visualisasi Penting

Mengapa harus melalui usaha menggambar ini? Deskripsi tekstual tentang logika sering kali ambigu. Kalimat seperti ‘Sistem memeriksa apakah pengguna sudah masuk sebelum menampilkan dasbor’ meninggalkan pertanyaan: Bagaimana jika mereka belum? Apakah akan dialihkan? Apakah menampilkan kesalahan? Apakah tetap di halaman yang sama?

Diagram status menghilangkan ambiguitas ini. Ini memaksa Anda untuk mendefinisikan selain itukasus secara eksplisit. Jika Anda tidak bisa menggambar panah untuk kasus selain itumaka Anda belum memiliki desain yang lengkap.

Selain itu, diagram status sangat baik untuk pengujian. Anda dapat membuat kasus uji untuk setiap transisi. Jika diagram menunjukkan transisi dari Menganggur ke Pemrosesan, maka harus ada kasus uji yang memverifikasi perpindahan ini. Ini memastikan cakupan kode tinggi dan kesalahan logika tertangkap lebih awal.

🔧 Alat dan Implementasi

Anda tidak perlu perangkat lunak mahal untuk membuat diagram ini. Banyak editor ringan mendukung notasi standar. Saat memilih alat, cari fitur-fitur berikut:

- Antarmuka Seret dan Letakkan:Manipulasi node dan tepi yang mudah.

- Pilihan Ekspor:Kemampuan mengekspor sebagai SVG, PNG, atau PDF untuk dokumentasi.

- Generasi Kode:Beberapa alat dapat menghasilkan kode kerangka untuk FSM, menghemat waktu implementasi.

- Kolaborasi:Pengeditan real-time memungkinkan tim untuk membangun diagram bersama-sama.

Ingat, alat tersebut bersifat sekunder dibandingkan logika. Sketsa yang digambar tangan di papan tulis lebih baik daripada diagram yang rapi namun memiliki logika yang salah. Mulailah dengan yang sederhana.

🧠 Ringkasan Poin-Poin Utama

Pemodelan Mesin State Hingga batas adalah keterampilan yang meningkatkan keandalan sistem. Dengan memvisualisasikan alur kontrol, Anda mengurangi bug dan meningkatkan komunikasi. Ingat prinsip-prinsip utama ini:

- Satu State pada Suatu Saat:Pastikan sistem tidak pernah berada dalam dua keadaan yang saling bertentangan secara bersamaan.

- Transisi yang Jelas:Setiap perpindahan harus memiliki pemicu dan tujuan.

- Jalur Kesalahan:Rancang untuk kegagalan. Kemana alur bergerak ketika sesuatu gagal?

- Kesederhanaan:Gunakan simbol standar dan label yang jelas. Hindari kerumitan.

Diagram state bukan hanya untuk para teoritis. Mereka adalah alat praktis bagi siapa saja yang membangun perangkat lunak, perangkat keras, atau proses bisnis. Dengan menguasai bahasa visual dari state, Anda mendapatkan kendali atas kompleksitas tanpa perlu memahami matematika di baliknya. Fokus pada alur, peristiwa, dan hasilnya. Sisanya akan mengikuti secara alami.