Membangun sistem perangkat lunak yang dapat diandalkan membutuhkan lebih dari sekadar menulis kode yang fungsional. Ini menuntut pemahaman yang jelas tentang bagaimana sistem berperilaku dalam berbagai kondisi. Diagram Mesin Status, yang sering disebut hanya sebagai Diagram Status, memberikan gambaran rancangan untuk perilaku ini. Mereka memetakan mode-mode berbeda yang dapat diisi oleh sistem serta aturan yang mengatur transisi antar mereka. Namun, seiring sistem menjadi lebih kompleks, kemungkinan terjadinya kesalahan logika meningkat. Mengevaluasi masalah ini membutuhkan pendekatan terstruktur, wawasan mendalam terhadap logika dasar, serta eliminasi variabel secara sistematis.

Panduan ini menjelaskan strategi-strategi penting untuk mengidentifikasi dan menyelesaikan kesalahan logika dalam arsitektur berbasis status. Dengan memahami anatomi transisi status dan jebakan umum, insinyur dapat menjaga integritas sistem tanpa harus mengandalkan tebakan.

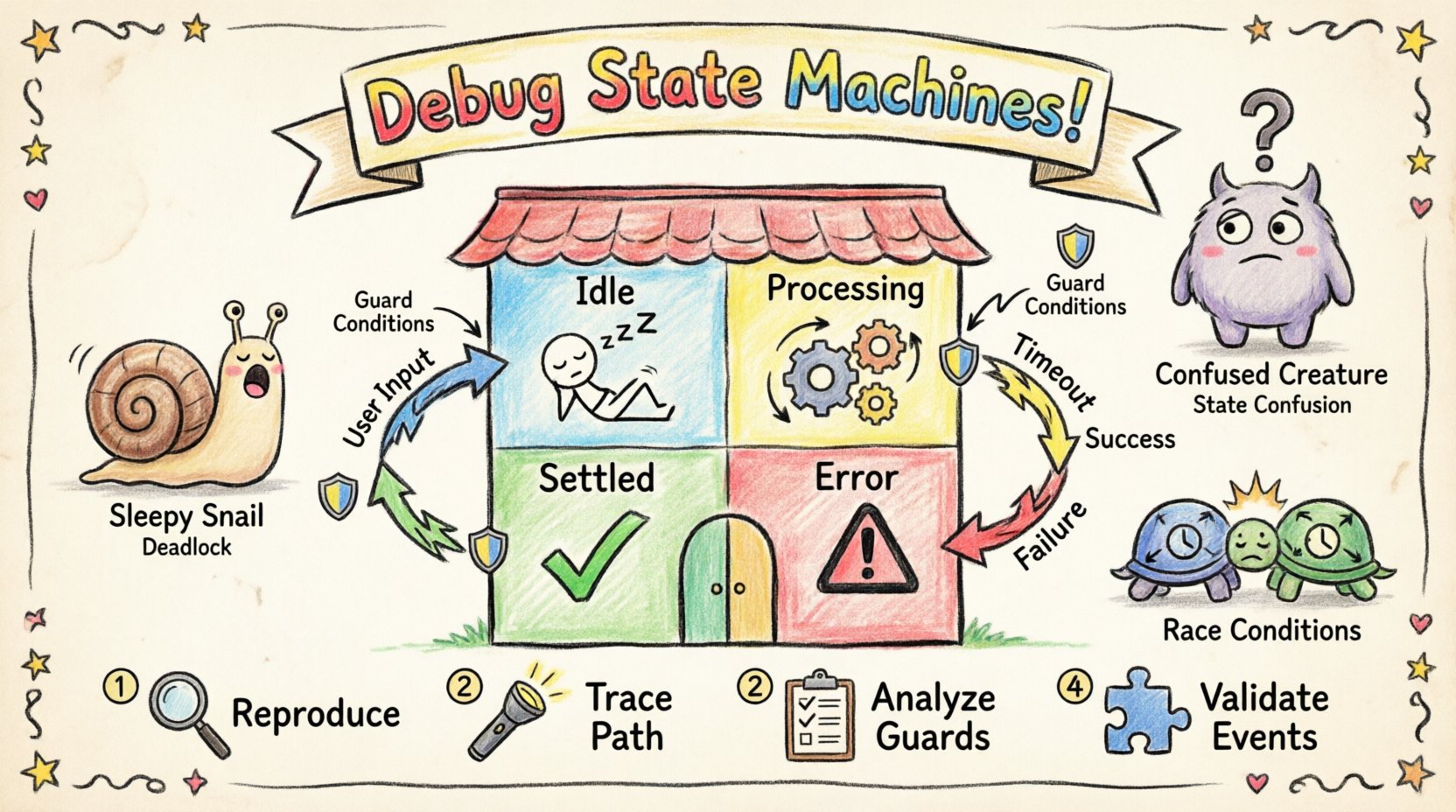

🔍 Memahami Anatomi Mesin Status

Sebelum melakukan pemecahan masalah, seseorang harus memahami komponen-komponen yang mendorong mesin status. Diagram status bukan sekadar representasi visual; ini adalah kontrak logis yang mendefinisikan siklus hidup sistem. Setiap elemen memiliki tujuan khusus dalam mengendalikan aliran dan data.

- Status: Mode atau kondisi berbeda yang dapat diisi oleh sistem. Contohnya termasuk Diam, Memproses, atau Kesalahan.

- Transisi: Jalur yang menghubungkan status. Transisi terjadi ketika peristiwa tertentu memicu perubahan dari satu status ke status lainnya.

- Peristiwa: Sinyal atau tindakan yang memicu transisi. Ini bisa berupa tindakan internal atau masukan eksternal.

- Pengekangan: Kondisi boolean yang dievaluasi selama transisi. Transisi hanya terjadi jika pengekangan bernilai benar.

- Aksi: Operasi yang dilakukan saat memasuki, keluar dari, atau selama transisi. Ini bisa mencakup pencatatan, pembaruan data, atau memicu layanan eksternal.

- Status Awal/Saat Akhir: Titik awal dan titik akhir dari siklus hidup.

Saat melakukan debugging, sangat penting untuk memverifikasi bahwa komponen-komponen ini berinteraksi dengan benar. Kesalahan logika sering berasal dari ketidaksesuaian antara perilaku yang diharapkan yang didefinisikan dalam diagram dan perilaku aktual di lingkungan runtime.

🚨 Kesalahan Logika Umum dan Gejala-Gejalanya

Sistem yang kompleks sering mengalami jenis-jenis kegagalan logika tertentu. Mengenali gejala sejak dini dapat menghemat waktu signifikan selama proses debugging. Tabel di bawah ini mengelompokkan masalah umum, gejala yang dapat diamati, serta kemungkinan akar penyebabnya.

| Jenis Kesalahan | Gejala | Akar Penyebab |

|---|---|---|

| Transisi Palsu | Sistem berpindah ke keadaan yang tidak terduga tanpa pemicu yang jelas. | Kondisi penjagaan yang hilang atau penangan event yang tumpang tindih. |

| Kebuntuan | Sistem berhenti dan tidak merespons input yang valid. | Tidak ada transisi keluar dari keadaan tertentu untuk peristiwa tertentu. |

| Keadaan yang Tidak Dapat Dijangkau | Beberapa keadaan tidak pernah dimasuki selama operasi normal. | Jalur masuk yang salah atau logika yang melewati keadaan tertentu. |

| Kerancuan Keadaan | Sistem berperilaku berbeda dalam keadaan yang sama tergantung pada sejarahnya. | Gagal mereset konteks atau mengelola keadaan sejarah dengan benar. |

| Kondisi Persaingan Paralel | Tindakan yang saling bertentangan terjadi secara bersamaan dalam keadaan paralel. | Kurangnya sinkronisasi antara sub-mesin paralel. |

🧪 Metodologi Debugging Langkah demi Langkah

Menyelesaikan masalah mesin keadaan memerlukan alur kerja yang disiplin. Perbaikan sementara sering kali menimbulkan bug baru. Ikuti pendekatan sistematis ini untuk mengisolasi dan memperbaiki kesalahan logika.

1. Replikasi Masalah

Sebelum mencoba memperbaiki, Anda harus dapat mereplikasi kesalahan dengan andal. Jika masalah bersifat sesekali, catat urutan kejadian yang menyebabkan kegagalan.

- Identifikasi input atau peristiwa khusus yang memicu perilaku yang salah.

- Catat keadaan sistem saat ini sebelum peristiwa terjadi.

- Catat keadaan yang dimasuki sistem setelah peristiwa terjadi.

- Periksa apakah masalah terjadi secara konsisten atau hanya dalam kondisi tertentu (misalnya, nilai data tertentu).

2. Lacak Jalur Eksekusi

Gunakan mekanisme pencatatan untuk melacak jalur eksekusi. Setiap transisi harus dicatat dengan konteks yang relevan.

- Pencatatan Masuk/Keluar:Catat saat suatu keadaan dimasuki dan ditinggalkan.

- Pencatatan Transisi:Catat peristiwa yang memicu transisi.

- Evaluasi Penjagaan:Catat apakah kondisi penjagaan lulus atau gagal dan mengapa.

- Pencatatan Tindakan:Catat saat tindakan dieksekusi dan outputnya.

Data ini menciptakan garis waktu kejadian. Bandingkan garis waktu ini dengan diagram status. Cari ketidaksesuaian di mana kode menyimpang dari desain.

3. Analisis Kondisi Penjaga

Kondisi penjaga sering menjadi sumber kesalahan logika. Suatu transisi mungkin tampak tersedia dalam diagram, tetapi kondisi tersembunyi mencegahnya dipicu.

- Ulas semua kondisi penjaga yang terkait dengan transisi yang bermasalah.

- Verifikasi bahwa variabel yang digunakan dalam kondisi penjaga sesuai dengan data yang tersedia pada saat kejadian.

- Periksa adanya efek samping dalam evaluasi kondisi penjaga yang mungkin mengubah status secara tak terduga.

- Pastikan kondisi penjaga tidak terlalu ketat, sehingga menghalangi transisi yang sah.

4. Validasi Penanganan Acara

Acara adalah pemicu perubahan. Jika suatu acara tidak ditangani dengan benar, sistem dapat mengabaikannya atau menanganinya dalam status yang salah.

- Periksa apakah nama acara cocok persis antara sumber dan mesin status.

- Verifikasi bahwa acara dikirim ke instance mesin status yang benar.

- Pastikan acara tidak dikonsumsi oleh status induk ketika status anak yang seharusnya menanganinya.

- Konfirmasi bahwa antrian acara memproses acara dalam urutan yang diharapkan.

🔄 Penanganan Konkurensi dan Status Paralel

Mesin status canggih sering menggunakan status konkuren. Ini memungkinkan beberapa mesin status independen berjalan secara bersamaan dalam suatu status komposit. Meskipun kuat, ini menimbulkan kompleksitas terkait sinkronisasi dan berbagi data.

1. Titik Sinkronisasi

Dalam lingkungan konkuren, transisi harus disinkronkan untuk mencegah kondisi ras. Suatu transisi dalam satu status paralel mungkin tergantung pada penyelesaian transisi dalam status lain.

- Tentukan batas sinkronisasi yang jelas di mana status paralel harus sejalan.

- Gunakan bendera atau variabel status untuk menunjukkan kesiapan cabang paralel.

- Pastikan status akhir dalam cabang paralel tercapai sebelum status komposit selesai.

2. Integritas Data Bersama

Status paralel sering mengakses sumber daya bersama. Jika dua status mengubah data yang sama secara bersamaan, korupsi dapat terjadi.

- Terapkan mekanisme penguncian saat mengakses variabel status bersama.

- Gunakan struktur data yang tidak dapat diubah jika memungkinkan untuk mencegah modifikasi yang tidak disengaja.

- Audit semua fungsi tindakan untuk menentukan apakah mereka mengubah status global atau bersama.

🛡️ Teknik Verifikasi dan Validasi

Debugging bersifat reaktif; verifikasi bersifat proaktif. Menerapkan strategi untuk memvalidasi mesin status sebelum penyebaran mengurangi beban pemecahan masalah.

1. Analisis Statis

Alat analisis statis dapat memindai definisi diagram status tanpa mengeksekusi kode. Mereka dapat mengidentifikasi masalah struktural.

- Periksa adanya status yang tidak dapat dijangkau.

- Identifikasi transisi yang tidak dapat dipicu oleh peristiwa apa pun.

- Verifikasi bahwa semua status memiliki jalur keluar yang valid.

- Pastikan semua peristiwa ditangani (tidak ada kesalahan peristiwa yang tidak ditangani).

2. Pemeriksaan Model

Pemeriksaan model melibatkan verifikasi matematis bahwa mesin status memenuhi sifat-sifat tertentu. Ini sangat berguna untuk sistem-sistem kritis terhadap keselamatan.

- Tentukan sifat-sifat seperti ‘sistem tidak pernah memasuki keadaan terkunci’.

- Jalankan algoritma untuk memverifikasi sifat-sifat ini terhadap graf transisi status.

- Gunakan alat-alat ini untuk memvalidasi skenario konkurensi yang kompleks.

3. Pengujian Unit untuk Mesin Status

Setiap status dan transisi harus diuji secara independen sebisa mungkin.

- Tulis pengujian yang menempatkan sistem pada status tertentu dan memicu peristiwa tertentu.

- Tegaskan bahwa sistem berpindah ke status berikutnya yang benar.

- Tegaskan bahwa tindakan yang diharapkan dipicu.

- Uji kondisi batas, seperti memicu peristiwa dalam status di mana tidak boleh diizinkan.

📝 Dokumentasi untuk Pemeliharaan Masa Depan

Mesin status yang sulit dipahami sulit didebug. Dokumentasi yang jelas memastikan insinyur masa depan dapat menangani masalah secara efektif tanpa harus membalikkan logika.

- Komentari Kode:Tambahkan komentar inline yang menjelaskan transisi yang kompleks atau kondisi penjaga yang tidak jelas.

- Pertahankan Diagram:Jaga agar diagram status visual tetap sinkron dengan kode. Diagram yang usang merupakan kerugian.

- Dokumentasikan Kasus Tepi:Catat keterbatasan yang diketahui atau skenario khusus yang dikelola secara berbeda oleh mesin.

- Kontrol Versi:Anggap definisi status sebagai kode. Gunakan kontrol versi untuk melacak perubahan logika seiring waktu.

⚙️ Adegan Dunia Nyata: Pipeline Pemrosesan Pembayaran

Pertimbangkan sistem pemrosesan pembayaran. Mesin status mengelola siklus hidup transaksi:Dimulai, Diberi Otorisasi, Tertagih, atau Gagal.

Bayangkan sebuah skenario di mana transaksi memasuki status Tertagih tetapi basis data menunjukkan bahwa statusnya masih Diberi Otorisasi. Ini adalah kesalahan ketidaksesuaian status klasik.

- Diagnosis: Transisi dari Diberi Otorisasi ke Tertagih dipicu, tetapi logika pembaruan status gagal menyetujui perubahan ke penyimpanan permanen.

- Dampak: Pengguna melihat sukses, tetapi backend mengharapkan dana tetap direservasi.

- Perbaikan: Terapkan pembungkus transaksi yang memastikan pembaruan status dan komit basis data terjadi secara atomik.

- Pencegahan: Tambahkan pekerjaan penyesuaian yang memeriksa status mesin status terhadap status basis data secara berkala.

🔧 Alat Pemecahan Masalah Lanjutan

Meskipun pelacakan manual efektif, alat tertentu dapat mempercepat proses debugging.

- Pemvisualisasi Status Interaktif: Alat yang memungkinkan Anda melangkah melalui status secara visual secara real-time.

- Pengumpul Log: Sistem pencatatan terpusat yang memungkinkan penyaringan berdasarkan ID status atau jenis peristiwa.

- Protokol Debug: Antarmuka yang memungkinkan sistem eksternal untuk menanyakan status saat ini dari mesin tanpa harus memulai ulang.

- Lingkungan Simulasi:Lingkungan sandboxing di mana Anda dapat memutar ulang urutan peristiwa untuk mereproduksi bug secara aman.

🧠 Beban Kognitif dan Kompleksitas Status

Ketika jumlah status meningkat, beban kognitif yang dibutuhkan untuk mempertahankan logika tumbuh secara eksponensial. Ini dikenal sebagai masalah ledakan status.

- Modularisasi:Pecah mesin status besar menjadi mesin sub yang lebih kecil dan mudah dikelola.

- Abstraksi:Gunakan status komposit untuk menyembunyikan kompleksitas dari logika tingkat tinggi.

- Batas:Batasi secara ketat jumlah status bersamaan untuk mengurangi beban sinkronisasi.

- Refaktor:Secara rutin tinjau diagram status untuk mengidentifikasi status yang berulang atau tumpang tindih.

🛑 Penanganan Masukan yang Tidak Terduga

Sistem yang tangguh harus mampu menangani masukan yang tidak didefinisikan dalam diagram status. Ini sering disebut sebagai “Status Kesalahan”.

- Transisi Default:Tentukan transisi penangkap semua untuk peristiwa yang terjadi dalam status yang tidak terduga.

- Pencatatan:Catat peristiwa yang tidak terduga dengan tingkat keparahan tinggi untuk memberi peringatan kepada pengembang.

- Pemulihan:Pastikan sistem dapat pulih dari status kesalahan, bukan mengalami kegagalan.

- Pemberitahuan:Beritahu pengguna atau sistem pemantauan ketika terjadi peristiwa yang tidak terduga.

📊 Metrik untuk Kesehatan Mesin Status

Untuk menjaga sistem tetap sehat, lacak metrik khusus yang terkait dengan mesin status.

- Frekuensi Transisi:Seberapa sering transisi tertentu terjadi. Perubahan mendadak bisa menjadi indikasi adanya bug.

- Durasi Status:Berapa lama sistem berada dalam status tertentu. Durasi panjang bisa menjadi indikasi terjadinya hambatan.

- Tingkat Kesalahan: Persentase kejadian yang menghasilkan transisi kesalahan.

- Jumlah Kematian Terkunci: Jumlah kali sistem memasuki keadaan tanpa transisi keluaran.

🚀 Kesimpulan tentang Integritas Sistem

Menjaga integritas mesin keadaan adalah proses yang berkelanjutan. Ini membutuhkan kewaspadaan, dokumentasi yang jelas, dan pemahaman mendalam terhadap alur logika. Dengan mengikuti metodologi yang diuraikan di atas, insinyur dapat secara efektif mendiagnosis kesalahan logika dan memastikan sistem kompleks berperilaku secara terduga.

Ingat bahwa tujuannya bukan hanya memperbaiki bug yang sedang terjadi, tetapi juga meningkatkan ketahanan arsitektur secara keseluruhan. Mesin keadaan yang dirancang dengan baik bersifat self-documenting dan tahan terhadap perubahan. Luangkan waktu pada tahap desain untuk mengurangi biaya pemecahan masalah di kemudian hari.

Terapkan prinsip-prinsip ini secara konsisten. Tinjau diagram Anda secara rutin. Uji transisi Anda secara menyeluruh. Dengan disiplin, Anda dapat mengelola kompleksitas dan menghasilkan perangkat lunak yang stabil dan handal.