Mendesain sistem yang kompleks membutuhkan lebih dari sekadar menggambar kotak dan panah. Ini menuntut pendekatan ketat dalam verifikasi logika. Saat membangun mesin state, representasi visual sering kali menyembunyikan kelemahan mendasar yang baru muncul saat eksekusi berlangsung. Validasi diagram state berfungsi sebagai pemeriksaan kritis antara desain dan peluncuran. Proses ini memastikan bahwa setiap transisi, peristiwa, dan kondisi penjaga berfungsi sesuai harapan dalam kondisi dunia nyata.

Tanpa validasi yang menyeluruh, sistem berisiko mengalami deadlock, state yang terbengkalai, atau perilaku yang tidak dapat diprediksi. Panduan ini mengeksplorasi metodologi yang diperlukan untuk memverifikasi integritas logika state. Kami akan meninjau bagaimana mengidentifikasi kelemahan struktural, menguji kasus ekstrem, dan mempertahankan konsistensi sepanjang siklus pengembangan.

🧩 Memahami Anatomis Diagram State

Sebelum terjun ke dalam validasi, sangat penting untuk memahami komponen-komponen yang sedang divalidasi. Diagram state adalah model perilaku yang menggambarkan bagaimana sistem bereaksi terhadap peristiwa. Diagram ini terdiri dari beberapa elemen kunci yang harus ditinjau secara ketat selama proses tinjauan.

- State: Ini mewakili mode operasi yang berbeda yang dapat diisi oleh sistem. Setiap state harus memiliki definisi yang jelas tentang apa yang sedang dilakukan sistem saat berada dalam mode tersebut.

- Transisi: Ini adalah jalur yang menghubungkan state. Mereka menunjukkan bagaimana sistem berpindah dari satu kondisi ke kondisi lainnya.

- Peristiwa: Ini adalah pemicu yang menyebabkan terjadinya transisi. Bisa berupa input pengguna, sinyal sistem, atau kejadian berbasis waktu.

- Penjaga: Ini adalah kondisi boolean yang harus bernilai benar sebelum transisi dapat terjadi.

- Aksi: Ini adalah tugas-tugas yang dieksekusi saat memasuki, keluar dari, atau selama transisi state.

Setiap elemen ini berinteraksi secara dinamis. Perubahan di satu area sering kali memengaruhi seluruh alur. Validasi memastikan bahwa interaksi ini tetap stabil dan logis.

⚠️ Biaya dari Logika yang Tidak Valid

Mengapa harus meluangkan waktu untuk validasi? Konsekuensi dari melewatkan langkah ini bisa sangat serius. Dalam rekayasa perangkat lunak, kesalahan logika pada mesin state sering menyebabkan kegagalan sistem, kerusakan data, atau kerentanan keamanan. Berbeda dengan kesalahan perhitungan sederhana, kelemahan mesin state sering bersifat non-deterministik, sehingga sulit diperbaiki setelah peluncuran.

Bayangkan sebuah aplikasi perbankan di mana status transaksi berpindah dariPemrosesan ke Selesai. Jika validasi lemah, gangguan jaringan bisa membuat sistem berada dalam keadaan ‘gantung’. Pengguna tidak melihat konfirmasi, namun dana mungkin sudah terpotong. Skenario ini menunjukkan perlunya validasi yang kuat.

Mode Kegagalan Umum

- Deadlock: Sistem mencapai keadaan di mana tidak ada transisi valid yang mungkin, sehingga memfreeze proses.

- State yang Tidak Valid: Sistem memasuki state yang tidak didefinisikan atau secara logika mustahil.

- State yang Tidak Dapat Dicapai: Beberapa state ada dalam diagram tetapi tidak pernah dapat dicapai dari state awal.

- Transisi yang Hilang: Suatu peristiwa terjadi dalam suatu keadaan, tetapi tidak ada transisi yang menanganinya, mengakibatkan perilaku yang tidak terdefinisi.

- Ketergantungan Melingkar:Keadaan berpindah dalam lingkaran tanpa kondisi penghentian, menyebabkan pemrosesan tak terbatas.

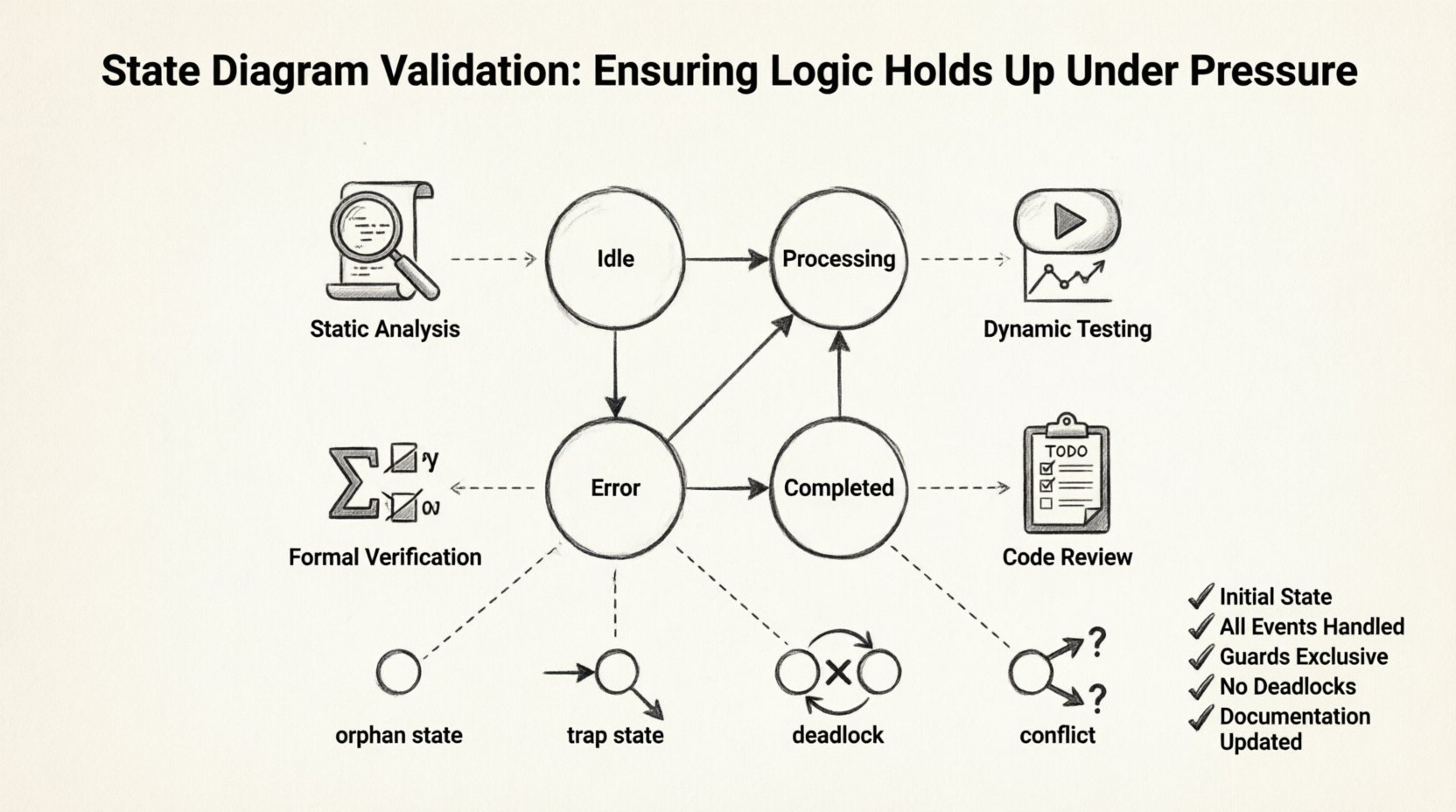

🔍 Metodologi Validasi

Validasi bukan satu langkah tunggal tetapi proses berlapis. Teknik-teknik yang berbeda melayani tujuan yang berbeda. Strategi yang komprehensif menggabungkan analisis statis dengan pengujian dinamis.

1. Analisis Statik dan Tinjauan

Analisis statik melibatkan tinjauan diagram tanpa mengeksekusi kode. Ini sering menjadi garis pertahanan pertama. Anggota tim meninjau diagram secara berurutan untuk memverifikasi alur logika.

- Pemeriksaan Konsistensi: Pastikan semua keadaan memiliki titik awal dan akhir yang didefinisikan.

- Pemeriksaan Kelengkapan: Verifikasi bahwa setiap peristiwa dalam setiap keadaan memiliki transisi yang sesuai.

- Pemeriksaan Keterbacaan: Pastikan diagram dapat dipahami oleh pengembang lain dan pemangku kepentingan.

Metode ini bergantung pada keahlian manusia. Ini efektif untuk menangkap kesalahan struktural tetapi dapat melewatkan interaksi runtime yang kompleks.

2. Pengujian Dinamis dan Simulasi

Pengujian dinamis melibatkan simulasi mesin keadaan dengan berbagai input. Pendekatan ini memvalidasi bahwa logika tetap kuat saat sistem benar-benar berjalan.

- Cakupan Jalur: Berusaha menelusuri setiap jalur yang mungkin dalam diagram.

- Pengujian Batas: Uji transisi yang terjadi pada batas kondisi penjaga.

- Pengujian Beban Tinggi: Sisipkan peristiwa berfrekuensi tinggi untuk melihat apakah mesin keadaan menangani konkurensi dengan benar.

Alat otomasi dapat membantu dalam menghasilkan kasus uji berdasarkan struktur diagram. Namun, skenario pengujian harus dirancang secara hati-hati agar mencakup persyaratan logika bisnis.

3. Verifikasi Formal

Untuk sistem kritis, metode verifikasi formal dapat digunakan. Teknik matematis ini membuktikan bahwa mesin keadaan memenuhi sifat-sifat tertentu, seperti keamanan atau kelangsungan.

- Sifat Keamanan:Memastikan bahwa keadaan buruk tidak pernah tercapai.

- Sifat Kelangsungan:Memastikan bahwa sistem pada akhirnya mencapai keadaan yang diinginkan.

Meskipun kuat, verifikasi formal membutuhkan pengetahuan dan alat khusus. Umumnya hanya digunakan untuk domain yang kritis terhadap keselamatan seperti penerbangan atau perangkat medis.

📊 Perbandingan Teknik Validasi

Memahami kekuatan dan kelemahan masing-masing metode membantu dalam memilih pendekatan yang tepat untuk proyek Anda.

| Teknik | Biaya | Kedalaman Cakupan | Paling Cocok Digunakan Untuk |

|---|---|---|---|

| Pemantauan Manual | Rendah | Dangkal | Fase desain awal, tinjauan konseptual |

| Pengujian Dinamis | Sedang | Dalam | Fase integrasi, pengujian regresi |

| Verifikasi Formal | Tinggi | Komprehensif | Sistem keselamatan kritis, persyaratan keandalan tinggi |

| Ulasan Kode | Sedang | Sedang | Memverifikasi bahwa implementasi sesuai dengan desain |

🚫 Mendeteksi Kekeliruan Struktural Umum

Pola-pola tertentu sering menunjukkan masalah yang mendasar. Mengenali pola-pola ini selama validasi dapat menghemat waktu debugging yang signifikan di kemudian hari.

1. Status Yatim

Status yatim adalah status yang tidak memiliki transisi masuk kecuali status awal. Jika sistem tidak dapat memasuki status ini melalui alur normal, kemungkinan besar merupakan kesalahan desain.

Langkah Validasi: Lacak mundur dari setiap status ke simpul awal. Jika suatu status terisolasi, verifikasi apakah status tersebut memang dimaksudkan tidak dapat diakses atau apakah transisi yang hilang.

2. Status Perangkap

Keadaan perangkap adalah keadaan di mana, setelah dimasuki, sistem tidak dapat keluar. Hal ini sering disebabkan oleh transisi keluar yang hilang.

Langkah Validasi: Periksa setiap keadaan untuk tepi keluar. Jika suatu keadaan tidak memiliki keluaran, tentukan apakah itu keadaan akhir atau kesalahan.

3. Konflik

Konflik terjadi ketika beberapa transisi mungkin terjadi untuk peristiwa yang sama dari keadaan yang sama. Hal ini mengakibatkan perilaku yang tidak menentukan.

Langkah Validasi: Pastikan bahwa penjaga saling eksklusif. Jika dua transisi berbagi peristiwa, kondisi penjaga mereka tidak boleh tumpang tindih.

4. Kebuntuan

Kebuntuan terjadi ketika sistem memasuki keadaan yang tidak memiliki transisi valid untuk peristiwa saat ini.

Langkah Validasi: Simulasikan sistem dengan setiap peristiwa yang mungkin di setiap keadaan. Jika suatu peristiwa tidak memiliki penangan, maka diperlukan transisi default atau mekanisme penanganan kesalahan.

🔄 Integrasi dengan Alur Kerja Pengembangan

Validasi tidak boleh dianggap sebagai hal terakhir. Harus diintegrasikan ke dalam alur kerja pengembangan agar efektif.

- Pendekatan Desain-terlebih Dahulu: Tentukan diagram keadaan sebelum menulis kode. Ini memastikan arsitektur kuat sebelum implementasi dimulai.

- Kontrol Versi: Anggap diagram keadaan sebagai kode. Simpan di sistem kontrol versi untuk melacak perubahan seiring waktu.

- Ulasan Teman Sejawat: Harus ada beberapa orang yang memeriksa diagram sebelum disetujui. Perspektif yang berbeda menangkap kesalahan yang berbeda.

- Dokumentasi: Pertahankan diagram agar selaras dengan dokumentasi. Diagram yang usang menyebabkan kebingungan dan bug.

🛠️ Menjaga Integritas Logika Seiring Waktu

Sistem berkembang. Persyaratan berubah. Fitur baru ditambahkan. Setiap perubahan membawa risiko terhadap logika keadaan yang ada.

Analisis Dampak

Saat memodifikasi diagram keadaan, lakukan analisis dampak. Tentukan keadaan dan transisi mana yang terdampak oleh perubahan tersebut.

- Identifikasi Ketergantungan: Buat peta bagaimana fitur baru berinteraksi dengan keadaan yang sudah ada.

- Periksa Efek Samping: Pastikan transisi baru tidak merusak alur kerja yang sudah ada.

- Perbarui Dokumentasi: Refleksikan semua perubahan dalam diagram dan spesifikasi terkait.

Pemeriksaan Regresi Otomatis

Seiring sistem berkembang, pengujian manual menjadi tidak efisien. Terapkan pemeriksaan otomatis yang memverifikasi perilaku mesin status terhadap diagram.

- Pengujian Snapshot: Tangkap status sistem pada titik-titik tertentu dan bandingkan dengan nilai yang diharapkan.

- Pengujian Kontrak: Tentukan kontrak untuk transisi status dan terapkan dalam suite pengujian.

- Pemantauan: Gunakan pemantauan saat runtime untuk mendeteksi anomali status dalam lingkungan produksi.

📝 Praktik Terbaik untuk Diagram yang Jelas

Diagram yang jelas lebih mudah divalidasi. Kompleksitas menyembunyikan kesalahan. Kesederhanaan mengungkapkannya.

- Batasi Kompleksitas: Jika diagram menjadi terlalu padat, pecah menjadi mesin bawah atau status hierarkis.

- Gunakan Konvensi Penamaan: Beri nama status dan peristiwa secara konsisten. Nama yang jelas mengurangi ambiguitas.

- Kelompokkan Status yang Terkait: Kelompokkan secara visual status yang termasuk dalam area fungsional yang sama.

- Jaga agar Tetap Terkini: Diagram yang tidak sesuai dengan kode justru lebih buruk daripada tidak memiliki diagram sama sekali.

🧪 Membuat Daftar Periksa Validasi

Untuk memastikan konsistensi, buat daftar periksa untuk setiap ulasan diagram status.

| Item | Periksa |

|---|---|

| Status Awal Didefinisikan | Ya / Tidak |

| Status Akhir Didefinisikan | Ya / Tidak |

| Semua Peristiwa Ditangani | Ya / Tidak |

| Pengekangan Bersifat Eksklusif | Ya / Tidak |

| Tidak Ada Kebuntuan yang Hadir | Ya / Tidak |

| Tidak Ada State Terlantar | Ya / Tidak |

| Dokumentasi Diperbarui | Ya / Tidak |

Gunakan daftar periksa ini sebagai bagian wajib dari proses penandatanganan. Ini memberikan catatan nyata bahwa validasi telah dilakukan.

🔗 Hubungan Antara Desain dan Kode

Seringkali terdapat celah antara diagram visual dan implementasi sebenarnya. Celah ini adalah tempat kebanyakan bug bersembunyi.

Generasi Kode: Jika menggunakan alat generasi kode, validasi output yang dihasilkan terhadap diagram.

Ulasan Kode: Saat meninjau kode, periksa apakah implementasi sesuai dengan logika mesin status. Cari state yang dikodekan secara langsung yang melewati diagram.

Refactoring: Saat melakukan refactoring kode, perbarui diagram secara bersamaan. Jangan biarkan diagram berjauhan dari implementasi.

🌟 Skenario Dunia Nyata

Pertimbangkan sistem pemrosesan pesanan e-commerce. Pesanan bergerak melalui status seperti Dibuat, Dibayar, Dikirimkan, dan Dikirimkan.

Jika pengguna membatalkan pesanan saat pesanan berada dalam status Dikirimkan, diagram harus mendefinisikan cara menanganinya. Apakah kembali ke Diproses? Apakah berpindah ke Dibatalkan? Tanpa validasi, kode mungkin hanya mengabaikan peristiwa tersebut, menyebabkan pesanan berada dalam keadaan terjebak.

Pertimbangkan perangkat medis. Perangkat mungkin memiliki status seperti Tidak Aktif, Aktif, dan Kesalahan. Jika terjadi kesalahan, perangkat harus berpindah ke Kesalahan segera. Validasi memastikan transisi ini diprioritaskan dan tidak dapat diblokir oleh peristiwa lain.

📈 Mengukur Keberhasilan Validasi

Bagaimana Anda tahu apakah upaya validasi Anda berhasil? Lacak metrik dari waktu ke waktu.

- Kepadatan Kesalahan: Ukur jumlah bug yang terkait status per modul.

- Tingkat Cakupan: Lacak persentase status dan transisi yang tercakup oleh uji coba.

- Waktu Rata-Rata Pemulihan: Ukur seberapa cepat sistem pulih dari kesalahan status di produksi.

- Waktu Siklus Tinjauan: Pantau berapa lama waktu yang dibutuhkan untuk memvalidasi perubahan diagram.

Peningkatan metrik-metrik ini menunjukkan bahwa proses validasi sedang berkembang.

🛠️ Alat dan Otomasi

Meskipun tidak ada perangkat lunak tertentu yang direkomendasikan, industri menawarkan berbagai alat untuk membantu dalam validasi.

- Pengedit Diagram: Gunakan alat yang menerapkan aturan sintaks untuk diagram status.

- Rangkaian Pengujian: Integrasikan perpustakaan pengujian mesin status ke dalam rangkaian pengujian Anda.

- Penganalisis Statis: Gunakan alat yang memindai diagram untuk anomali struktural.

Otomasi mengurangi kesalahan manusia dan memungkinkan siklus validasi yang lebih sering.

🎓 Pelatihan dan Berbagi Pengetahuan

Validasi adalah keterampilan. Tim perlu pelatihan untuk menjadi ahli.

- Workshop: Adakan sesi tentang teori mesin status dan praktik terbaik.

- Templat: Buat templat untuk pola status umum agar konsistensi terjaga.

- Studi Kasus: Tinjau bug masa lalu yang berkaitan dengan logika status untuk memahami apa yang salah.

Membangun budaya kualitas memastikan bahwa validasi dianggap serius oleh semua pihak yang terlibat.

🏁 Pikiran Akhir tentang Integritas Logika

Membangun sistem yang dapat diandalkan adalah upaya berkelanjutan. Validasi diagram status adalah fondasi dari upaya ini. Dengan menerapkan teknik yang ketat, Anda dapat memastikan logika Anda tetap kuat di bawah tekanan. Investasi dalam validasi memberi manfaat besar dalam stabilitas dan kepercayaan.

Fokus pada detail. Periksa setiap transisi. Uji setiap kasus batas. Pertahankan diagram Anda. Tindakan-tindakan ini membentuk dasar sistem yang kuat. Dengan pendekatan yang disiplin, Anda dapat mengelola kompleksitas dan menghasilkan hasil berkualitas tinggi.