Mendesain sistem yang kuat membutuhkan lebih dari sekadar menghubungkan komponen secara visual; diperlukan verifikasi logika yang ketat. Saat membuat Diagram Aliran Data, representasi visual pergerakan informasi hanya sebaik logika yang mendorongnya. Kesalahan pada tahap desain ini dapat menimbulkan kegagalan operasional yang signifikan di kemudian hari. Panduan ini memberikan penjelasan mendalam tentang mengidentifikasi dan memperbaiki kesalahan logika dalam desain aliran untuk memastikan integritas data dan keandalan proses. 🧠

Memahami Dasar-dasar Desain Aliran 🏗️

Sebelum mengidentifikasi kesalahan, seseorang harus memahami arsitektur dari Diagram Aliran Data standar. Diagram ini memetakan pergerakan data melalui suatu sistem, menyoroti entitas eksternal, proses, penyimpanan data, dan aliran yang menghubungkannya. Tujuan utamanya adalah memvisualisasikan bagaimana informasi masuk, berubah, dan keluar dari suatu sistem. Ketika logika yang mengatur pergerakan ini rusak, arsitektur sistem yang dihasilkan menjadi tidak stabil.

Kesalahan logika berbeda dengan kesalahan sintaks. Kesalahan sintaks mencegah diagram digambar atau divalidasi secara teknis. Kesalahan logika berarti diagram digambar dengan benar tetapi merepresentasikan realitas yang mustahil atau tidak efisien. Misalnya, suatu proses bisa digambarkan menerima input tanpa output yang didefinisikan, atau data muncul dari kehampaan. Anomali ini mengganggu alur logika informasi. ⚙️

Memastikan diagram secara akurat mencerminkan aturan bisnis dan hukum konservasi data sangat penting. Setiap data yang masuk ke suatu proses harus diubah, disimpan, atau dipindahkan. Tidak boleh ada yang diciptakan atau dihancurkan tanpa mekanisme yang didefinisikan. Prinsip ini adalah fondasi konsistensi logika dalam desain aliran.

Kategori Kesalahan Logika yang Harus Diketahui 🔍

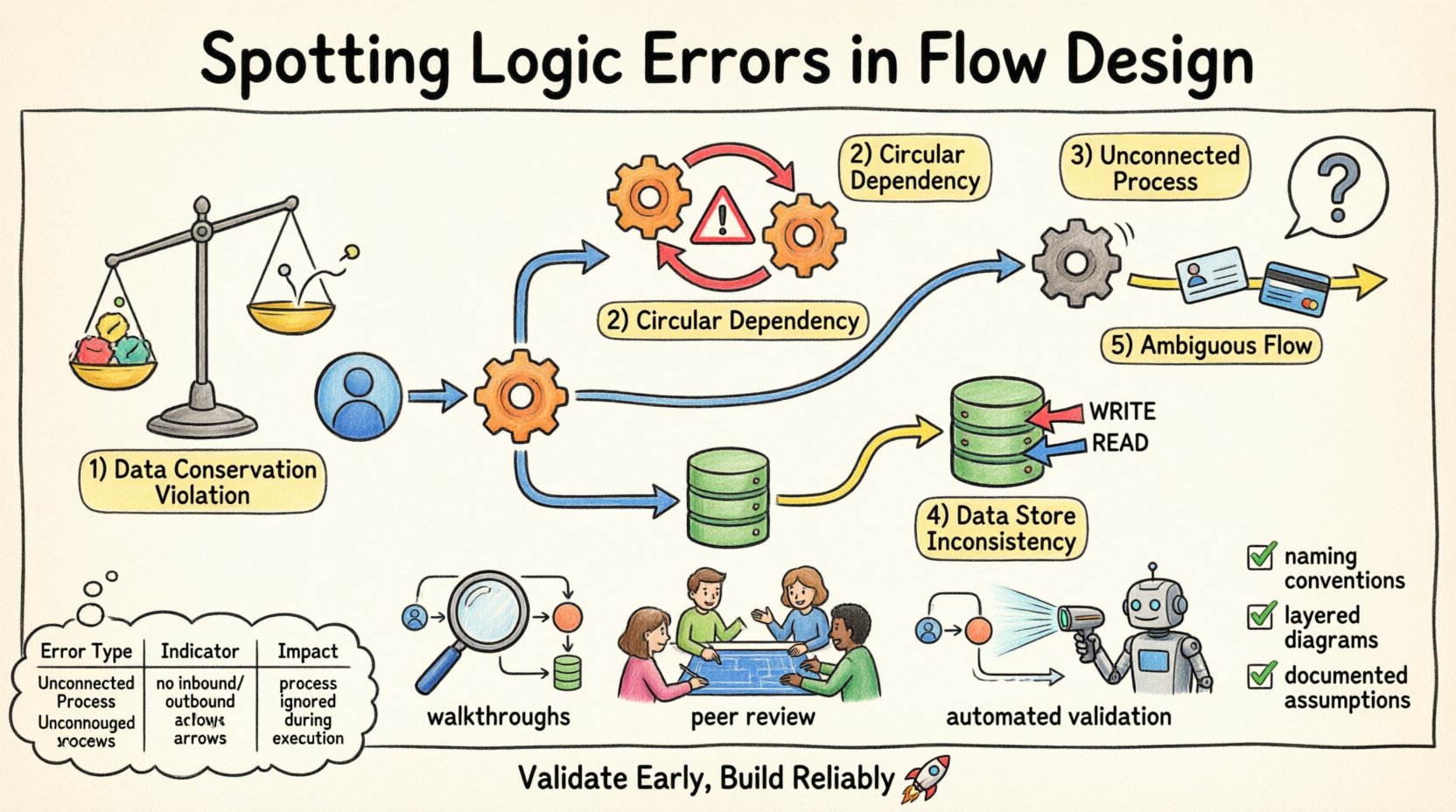

Kesalahan logika muncul dalam berbagai bentuk dalam desain aliran. Mengenali kategori-kategori ini membantu dalam tinjauan sistematis. Berikut adalah jenis-jenis ketidaksesuaian logika utama yang sering muncul pada tahap desain.

1. Pelanggaran Konservasi Data 📉

Hukum konservasi data menyatakan bahwa data tidak boleh diciptakan atau dihancurkan dalam suatu proses. Jika diagram aliran menunjukkan data muncul dari suatu proses tanpa sumber yang jelas, maka hukum ini dilanggar. Sebaliknya, jika data masuk ke proses dan menghilang tanpa disimpan atau dihasilkan, maka data tersebut hilang. Hal ini sering terjadi ketika desainer lupa menggambar panah output.

Misalnya, jika proses pesanan pelanggan menerima detail pesanan tetapi hanya menghasilkan bukti konfirmasi, informasi pembayaran hilang. Ini menunjukkan adanya celah dalam logika. Sistem tidak dapat berfungsi tanpa mempertimbangkan semua input dan output.

2. Ketergantungan Lingkar 🔄

Ketergantungan lingkar terjadi ketika Proses A memberikan data ke Proses B, yang kemudian memberikan data kembali ke Proses A tanpa langkah antara. Dalam diagram statis, ini tampak seperti lingkaran. Meskipun lingkaran ada dalam sistem berbasis waktu, dalam desain aliran logika, hal ini sering menunjukkan deadlock atau rekursi tak terbatas yang tidak dapat dipecahkan sistem.

Mengidentifikasi ini memerlukan pelacakan jalur data. Jika suatu proses bergantung pada output proses lain yang sedang menunggu proses pertama, aliran akan terhenti. Ini adalah kesalahan logika kritis yang menghentikan eksekusi sistem.

3. Proses yang Tidak Terhubung 🚫

Proses yang tidak terhubung adalah proses yang tidak memiliki aliran data masuk. Tanpa input, suatu proses tidak dapat dieksekusi. Ini adalah pulau logika. Demikian pula, proses yang tidak memiliki aliran keluar tidak memberikan kontribusi terhadap output keseluruhan sistem. Meskipun proses internal bisa ada tanpa output eksternal langsung, mereka harus pada akhirnya terhubung ke rantai yang mencapai penyimpanan data atau entitas eksternal.

Proses yang terisolasi menunjukkan desain yang tidak lengkap. Mereka mengonsumsi sumber daya tetapi tidak memberikan nilai. Menemukan ini memerlukan analisis koneksi setiap simpul dalam diagram.

4. Ketidaksesuaian Penyimpanan Data 🗄️

Penyimpanan data mewakili informasi yang tetap. Kesalahan logika muncul ketika proses membaca atau menulis ke penyimpanan data tanpa otorisasi atau konteks yang tepat. Misalnya, suatu proses bisa memperbarui catatan tanpa memverifikasi apakah pengguna memiliki izin, atau suatu proses bisa membaca data yang hanya ditulis oleh proses lain yang belum berjalan.

Masalah umum lainnya adalah penyimpanan data dibaca dan ditulis secara bersamaan oleh proses yang berbeda tanpa sinkronisasi. Ini menciptakan kondisi persaingan dalam model logika. Diagram harus menunjukkan jalur tulis dan baca yang jelas untuk menghindari ambiguitas.

5. Aliran Data yang Ambigu 🌫️

Aliran data harus diberi nama dan dijelaskan secara jelas. Aliran yang ambigu adalah aliran yang membawa berbagai jenis data tanpa perbedaan. Jika satu panah mewakili baik “ID Pengguna” maupun “Nomor Kartu Kredit”, logikanya rusak karena elemen data ini memiliki persyaratan keamanan dan pemrosesan yang berbeda.

Memisahkan aliran-aliran ini memastikan setiap informasi ditangani sesuai aturan khususnya. Ambiguitas menyebabkan kerentanan keamanan dan kesalahan pemrosesan di hilir.

| Jenis Kesalahan | Indikator | Dampak |

|---|---|---|

| Konservasi Data | Data muncul/hilang | Kehilangan atau kerusakan data |

| Ketergantungan Lingkar | Proses A → Proses B → Proses A | Deadlock sistem |

| Proses yang Tidak Terhubung | Tidak ada panah input atau output | Pemborosan sumber daya |

| Ketidaksesuaian Penyimpanan Data | Baca/tulis yang tidak terkendali | Masalah integritas data |

| Aliran yang Ambigu | Tipe data yang bercampur dalam satu aliran | Risiko keamanan |

Metodologi untuk Deteksi 🛡️

Setelah jenis kesalahan diketahui, langkah berikutnya adalah menetapkan metodologi untuk menemukannya. Tinjauan pasif sering kali tidak cukup. Diperlukan penyelidikan aktif terhadap diagram.

Panduan Langkah demi Langkah 🚶

Lakukan pemetaan mental terhadap diagram. Mulai dari entitas eksternal dan lacak data melalui setiap proses hingga ke penyimpanan data atau entitas lainnya. Ajukan pertanyaan di setiap simpul. Apakah proses ini memiliki cukup input untuk berjalan? Apakah menghasilkan output yang diharapkan? Jika saya mengeksekusi logika ini, data akan ke mana?

Pemetaan manual ini memaksa desainer untuk memvisualisasikan pergerakan data secara dinamis. Ini mengungkap celah yang terlewat oleh pemantauan statis. Jika pemetaan terhenti di suatu simpul, kemungkinan besar di situlah letak kesalahan logika.

Sesi Tinjauan Rekan Kerja 👥

Orang lain yang melihat diagram membawa perspektif baru. Peninjau dapat mengidentifikasi kesalahan yang telah diabaikan oleh desainer karena terlalu akrab. Dorong peninjau untuk mempertanyakan asumsi. Minta mereka menemukan aliran data yang tampak tidak perlu atau hilang.

Sesi tinjauan yang terstruktur mengurangi kemungkinan terlewat. Daftar periksa harus digunakan selama tinjauan ini untuk memastikan semua kategori kesalahan tercakup.

Aturan Validasi Otomatis 🤖

Meskipun perangkat lunak tertentu tidak disebutkan di sini, alat validasi logika dapat memindai diagram untuk kesalahan struktural. Alat ini dapat menandai simpul yang tidak terhubung, penyimpanan data yang hilang, atau referensi melingkar. Alat ini berfungsi sebagai garis pertahanan pertama terhadap inkonsistensi logika dasar.

Menggunakan pemeriksaan otomatis memungkinkan tim untuk fokus pada logika tingkat tinggi daripada sintaks struktural. Ini memastikan dasar yang kuat sebelum menambah kompleksitas.

Biaya Akibat Pengabaian Logika 💸

Mengapa hal ini penting? Kesalahan logika pada tahap desain adalah yang paling mahal untuk diperbaiki. Jika kesalahan logika ditemukan saat pengkodean, diperlukan penulisan ulang modul. Jika ditemukan setelah peluncuran, diperlukan perbaikan dan mungkin pemindahan data.

Bayangkan skenario di mana aliran data kehilangan langkah validasi. Hal ini memungkinkan data yang tidak valid memasuki sistem. Kemudian, laporan yang dihasilkan dari data ini menjadi tidak akurat. Bisnis membuat keputusan berdasarkan informasi yang salah. Biaya untuk membersihkan data ini dan memulihkan kepercayaan jauh lebih tinggi daripada biaya memperbaiki diagram dari awal.

Selain itu, kesalahan logika dapat menyebabkan pelanggaran keamanan. Jika suatu aliran memungkinkan data melewati pemeriksaan keamanan, informasi sensitif akan terbuka. Hal ini dapat mengakibatkan pelanggaran kepatuhan dan konsekuensi hukum. Pencegahan kesalahan ini bukan hanya tentang efisiensi; tetapi juga tentang manajemen risiko.

Strategi Pencegahan 🛡️

Pencegahan lebih baik daripada deteksi. Menerapkan standar dan praktik selama pembuatan desain aliran mengurangi kemungkinan terjadinya kesalahan dari awal.

Konvensi Penamaan yang Diseragamkan 🏷️

Tetapkan aturan penamaan yang ketat untuk proses, penyimpanan data, dan aliran. Nama proses harus berupa pasangan kata kerja-benda, seperti “Validasi Pesanan.” Nama aliran harus menggambarkan data, seperti “Detail Pesanan.” Konsistensi ini memudahkan identifikasi anomali. Jika suatu aliran bernama “Data,” kemungkinan besar terlalu samar dan harus ditinjau lebih ketat.

Penamaan yang konsisten juga membantu validasi otomatis. Skrip dapat menganalisis nama untuk memeriksa kepatuhan terhadap struktur logika.

Diagram Berlapis 📑

Pecah sistem yang kompleks menjadi beberapa tingkatan. Level 0 menampilkan proses tingkat tinggi. Level 1 mendekomposisi proses-proses tersebut menjadi sub-proses. Pendekatan hierarkis ini mencegah diagram menjadi kusut. Kekusutan menyembunyikan kesalahan logika.

Dengan memperbesar area tertentu, desainer dapat fokus pada logika subsistem tertentu tanpa kehilangan gambaran keseluruhan. Kesalahan lebih mudah terdeteksi dalam tampilan fokus.

Dokumentasi Asumsi 📝

Setiap diagram dibuat dengan asumsi. Dokumentasikan secara eksplisit. Jika suatu proses mengasumsikan data selalu tersedia, nyatakan asumsi tersebut. Jika suatu aliran menyiratkan keterlambatan waktu, catat hal itu. Dokumentasi ini memberikan konteks bagi peninjau. Ini menjelaskan mengapa pilihan logika tertentu dibuat.

Ketika asumsi didokumentasikan, mereka dapat dipertanyakan dan divalidasi terhadap kebutuhan bisnis. Ini mengurangi kemungkinan kesalahan logika tersembunyi tetap ada dalam desain akhir.

Daftar Periksa Validasi ✅

Sebelum menyelesaikan desain aliran, lakukan pemeriksaan daftar ini. Ini mencakup area penting di mana kesalahan logika biasanya tersembunyi.

- Kelengkapan Input: Apakah setiap proses memiliki setidaknya satu aliran masuk?

- Kelengkapan Output: Apakah setiap proses memiliki setidaknya satu aliran keluar?

- Keseimbangan Data: Apakah volume data tetap terjaga di seluruh proses?

- Tidak Ada Jalan Buntu: Apakah ada proses yang tidak menuju ke penyimpanan data atau entitas eksternal?

- Penamaan yang Jelas: Apakah semua aliran dan proses diberi nama secara deskriptif?

- Keamanan: Apakah aliran data sensitif secara jelas ditandai dan dilindungi secara logis?

- Sensitivitas Waktu: Apakah ada ketergantungan waktu yang secara jelas didefinisikan?

- Konsistensi: Apakah penyimpanan data sesuai dengan data yang digunakan dalam proses?

Memperhalus Desain 🎯

Setelah kesalahan ditemukan, proses penyempurnaan dimulai. Ini melibatkan modifikasi diagram untuk memperbaiki logika. Tidak selalu tentang menghapus elemen; terkadang justru tentang menambahkan koneksi yang hilang.

Sebagai contoh, jika suatu proses tidak memiliki output, tentukan di mana data harus dikirim. Tambahkan panah yang hilang ke penyimpanan data atau entitas yang sesuai. Jika terdapat ketergantungan melingkar, perkenalkan buffer atau antrian untuk memutus lingkaran tersebut. Ini mungkin berarti menambahkan langkah perantara dalam desain.

Penyempurnaan bersifat iteratif. Setelah melakukan perubahan, jalankan kembali panduan jalan dan daftar periksa. Pastikan logika baru dapat bertahan terhadap tinjauan ketat. Jangan mengasumsikan perbaikan selesai hingga diagram lulus semua tahap validasi.

Pikiran Akhir Mengenai Integritas Logis 💡

Integritas desain aliran menentukan keberhasilan sistem. Kesalahan logika bersifat halus namun merusak. Mereka melemahkan keandalan seluruh arsitektur. Dengan menerapkan metode deteksi yang ketat dan strategi pencegahan, desainer dapat membangun sistem yang berfungsi sesuai tujuan.

Perhatian terhadap detail pada tahap desain menghemat waktu, uang, dan usaha di tahap selanjutnya. Diagram yang telah divalidasi dengan baik adalah gambaran rancangan untuk sistem yang stabil. Memprioritaskan konsistensi logis memastikan data bergerak dengan benar, aman, dan efisien melalui organisasi. Pendekatan ini menghasilkan sistem yang tidak hanya berfungsi, tetapi juga tangguh terhadap perubahan. 🚀

Tetap fokus pada kejelasan dan kebenaran. Setiap panah penting. Setiap simpul berharga. Dengan mematuhi prinsip-prinsip ini, desain aliran menjadi aset yang dapat dipercaya bagi tim pengembangan.