Projektowanie maszyn stanów to ćwiczenie precyzji. Jedna nieprawidłowo umieszczona przejście lub niezdefiniowane zdarzenie może prowadzić do niestabilnego zachowania systemu. Gdy kod jest wykonywany, często śledzi diagram, ale sam diagram może ukrywać sprzeczności. Debugowanie diagramu stanów wymaga zmiany nastawienia od typowej inspekcji kodu w kierunku teorii grafów i weryfikacji logicznej. Niniejszy przewodnik przedstawia sposób identyfikacji i rozwiązywania ukrytych wad logiki w modelach maszyn stanów.

Niezależnie od tego, czy pracujesz z diagramami stanów UML, maszynami stanów skończonych (FSM) czy niestandardową logiką stanów, podstawowe wyzwania pozostają te same. Złożoność rośnie wraz z hierarchią, współbieżnością i stanami historii. Niniejszy artykuł skupia się na kluczowych strategiach weryfikacji tych modeli przed ich wdrożeniem w środowiskach produkcyjnych.

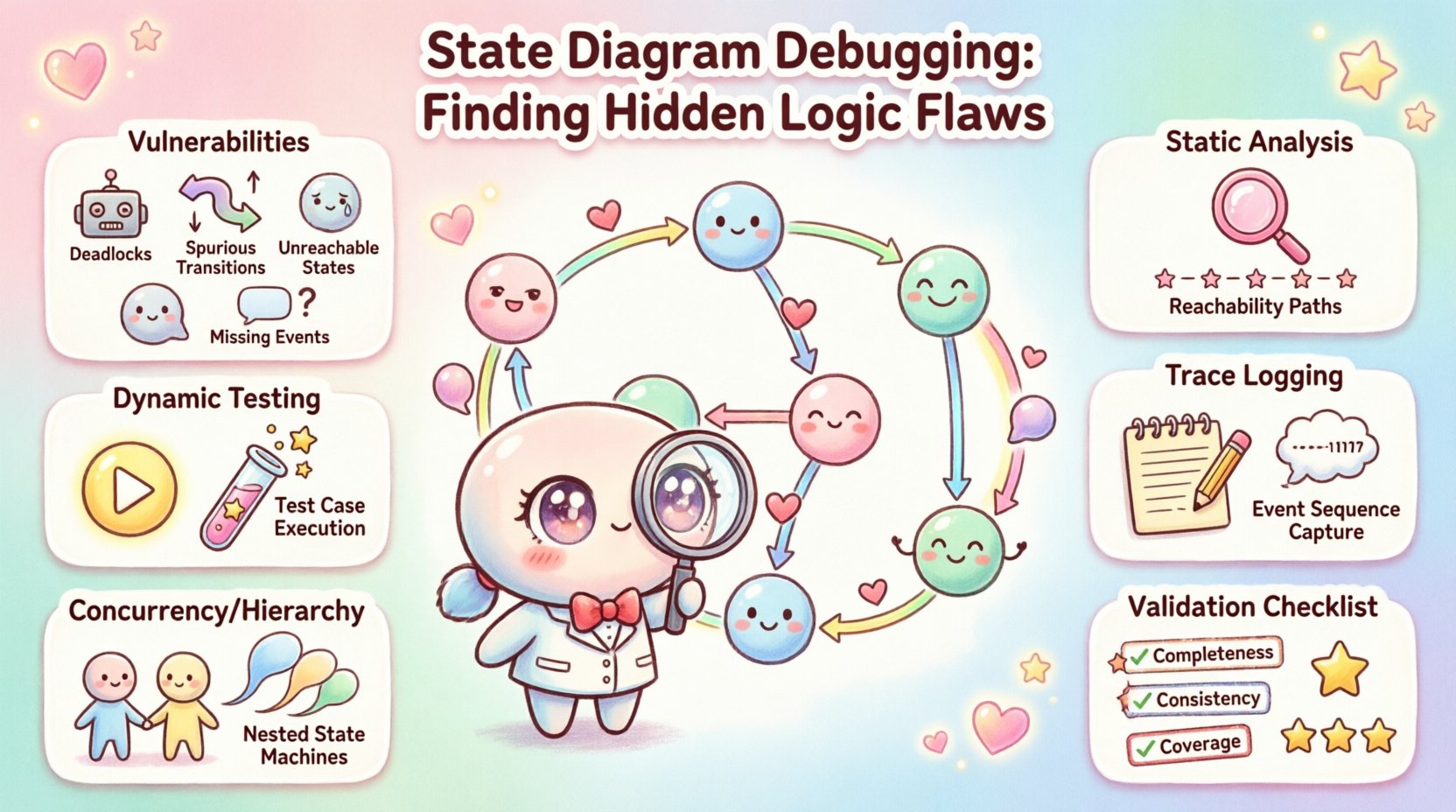

🧩 Zrozumienie wad maszyn stanów

Diagramy stanów to wizualne przedstawienia zachowania systemu. Choć zapewniają przejrzystość, wprowadzają również określone tryby awarii, które różnią się od błędów kodu proceduralnego. Te wady często wynikają z topologii grafu, a nie z implementacji obsługi zdarzeń.

Podczas debugowania należy najpierw szukać problemów z integralnością strukturalną. Maszyna stanów, która nie może osiągnąć stanu końcowego lub zawiesza się w pętli bez postępu, jest podstawowo uszkodzona. Poniżej przedstawiono główne kategorie błędów logicznych występujących w diagramach stanów.

- Zamknięcia (deadlocks): Stan, w którym dla bieżącego zdarzenia nie istnieją żadne przejścia wyjściowe, co powoduje zatrzymanie systemu.

- Nieuzasadnione przejścia: Zdarzenia, które wywołują niepożądane ścieżki z powodu niejednoznacznych stanów docelowych.

- Nieosiągalne stany: Stany, do których nie można dotrzeć ze stanu początkowego, co czyni je bezużytecznymi.

- Zbyteczne stany: Wiele stanów realizujących identyczne funkcje, co utrudnia konserwację.

- Brakujące zdarzenia: Sytuacje, w których system nie ma obsługi dla określonego wejścia w danym stanie.

- Błędy stanów historii: Błędy logiczne związane ze stanami historii głębokiej lub powierzchniowej, które przywracają niepoprawny kontekst.

Wczesne wykrywanie tych problemów zapobiega kosztownej refaktoryzacji w przyszłości. Proces debugowania obejmuje zarówno statyczną analizę modelu, jak i dynamiczne testowanie ścieżek wykonania.

🛠️ Metody analizy statycznej

Analiza statyczna polega na badaniu diagramu bez wykonywania ukrytej logiki. Ta faza jest kluczowa do wykrywania błędów topologii przed wygenerowaniem lub napisaniem jakiegokolwiek kodu. Celem jest weryfikacja własności matematycznych grafu stanów.

1. Analiza osiągalności

Każdy stan w poprawnie zbudowanym diagramie powinien być osiągalny z węzła początkowego. Aby to zweryfikować, prześledź ścieżkę od stanu początkowego do każdego innego stanu. Jeśli stan nie jest osiągalny, jest to artefakt projektowy, który nie ma żadnego znaczenia.

- Rozpocznij od Stan początkowy.

- Śledź wszystkie możliwe strzałki przejść.

- Zaznacz każdy odwiedzony stan.

- Porównaj zaznaczone stany z całkowitą liczbą stanów.

- Każdy niezaznaczony stan jest nieosiągalny.

Niedostępne stany często pojawiają się, gdy stan podrzędny jest zagnieżdżony w stanie złożonym, który nigdy nie jest wejściowy. W scenariuszach debugowania usuwanie tych stanów zmniejsza obciążenie poznawcze dla przyszłych utrzymujących system.

2. Pełność przejść

Każdy stan powinien definiować zachowanie dla oczekiwanych zdarzeń. Jeśli zdarzenie występuje w stanie, w którym nie zdefiniowano przejścia, zachowanie systemu jest nieokreślone. Jest to częsty powód awarii w czasie działania lub niezauważalnych błędów.

Podczas przeglądu schematu szukaj:

- Przejścia domyślne: Czy stan odpowiednio obsługuje nieoczekiwane dane wejściowe?

- Pokrycie zdarzeń: Czy wszystkie zarejestrowane wywołania interfejsu API lub działania użytkownika są przypisane do przejść?

- Warunki strażnika: Czy istnieją strażnicy, którzy zapobiegają jednoczesnemu wyzwoleniu wszystkich przejść, powodując zastój?

Wytrzymała maszyna stanów obsługuje scenariusze „a co, jeśli”. Jeśli warunek strażnika przejścia ma wartość fałsz, dokąd idzie przepływ? Jeśli nie ma alternatywy, system zatrzymuje się.

3. Wykrywanie cykli

Nieskończone pętle w maszynie stanów mogą zużywać zasoby lub zatrzymywać procesor. Choć niektóre pętle są celowe (np. oczekiwanie na dane wejściowe), inne są przypadkowe.

- Śledź ścieżki, które powracają do tego samego stanu bez zużywania czasu lub zdarzeń.

- Zidentyfikuj pętle oparte wyłącznie na warunkach strażnika, które nigdy się nie zmieniają.

- Upewnij się, że pętle mają mechanizm wyjścia, np. limit czasu lub sygnał zewnętrzny.

🧪 Testowanie dynamiczne i ścieżki wykonania

Analiza statyczna jest potężna, ale nie może symulować czasu i stanu środowiska uruchomieniowego. Testowanie dynamiczne polega na podawaniu zdarzeń do systemu i obserwacji rzeczywistych zmian stanu. To właśnie tutaj często ujawniają się ukryte błędy logiczne.

1. Testowanie pokrycia ścieżek

Celem jest wykonanie każdego możliwego przejścia co najmniej raz. Wymaga to zaprojektowania przypadków testowych, które zmuszają system do przejścia przez określone stany.

- Przypisz przypadki testowe do przejść na schemacie.

- Upewnij się, że testujesz ścieżkę negatywną (gdzie przejście nie powinno się wydarzyć).

- Zweryfikuj, czy system pozostaje w poprawnym stanie po zdarzeniu.

- Zapisz identyfikator stanu po każdym zdarzeniu, aby potwierdzić, że schemat odpowiada rzeczywistości.

2. Testowanie wytrzymałości przejść stanów

Szybkie, szybko następujące zdarzenia mogą ujawnić warunki wyścigu. Jeśli dwa zdarzenia przychodzą w krótkim odstępie czasu, czy maszyna stanów przetwarza je w poprawnej kolejności? Czy stan aktualizuje się atomowo?

- Wyślij zdarzenia o wysokiej częstotliwości do obsługi stanów.

- Obserwuj, czy system pomija stany lub przetwarza je w niepoprawnej kolejności.

- Sprawdź, czy stany pośrednie są widoczne, czy system od razu przechodzi do stanu końcowego.

3. Testowanie warunków brzegowych

Przypadki graniczne często ukrywają błędy logiki. Co się dzieje, gdy maszyna stanów znajduje się w stanie końcowym i otrzymuje dane wejściowe? Co się stanie, jeśli przejście zostanie wyzwolone natychmiast po wejściu do stanu?

- Zbadaj Akcja wejścia vs. Akcja wyjścia czasowanie.

- Zweryfikuj zachowanie podczas przejścia od stanu początkowego bezpośrednio do złożonego stanu podrzędnego.

- Sprawdź zachowanie, gdy stan historii jest wywoływany wielokrotnie.

🔎 Rejestrowanie śledzenia i korelacja zdarzeń

Gdy występuje błąd w środowisku produkcyjnym, diagram stanów jest Twoją mapą. Aby znaleźć wadę, potrzebujesz śladu. Wprowadzenie skutecznego mechanizmu rejestrowania jest kluczowe do debugowania maszyn stanów.

1. Rejestrowanie wejścia i wyjścia z stanu

Każdorazowo, gdy system wejście lub opuszcza stan, powinien zapisywać to zdarzenie. Dzięki temu uzyskujesz chronologię wykonywania.

- Zarejestruj Stan źródłowy.

- Zarejestruj Stan docelowy.

- Zarejestruj Zdarzenie wyzwalające.

- Zarejestruj Znacznik czasu i Dane kontekstowe.

Te dane pozwalają na odtworzenie ścieżki, którą system przebył przed wystąpieniem błędu.

2. Ocena warunków strażnika

Przejścia często zależą od warunków strażnika (warunków logicznych). Jeśli przejście nie powiedzie się, czy było to spowodowane fałszywym warunkiem strażnika, czy też nieznanym zdarzeniem?

- Zarejestruj wynik oceny każdego warunku strażnika.

- Zapisz zmienne używane w warunku.

- Określ, czy warunek warunku jest zbyt restrykcyjny.

Bez tej widoczności trudno rozróżnić błąd logiki w maszynie stanów od błędu logiki w danych sterujących warunkiem.

⚡ Obsługa współbieżności i hierarchii

Zaawansowane diagramy stanów wykorzystują regiony ortogonalne (współbieżność) i zagnieżdżone stany (hierarchia). Te funkcje dodają możliwości, ale również znaczną złożoność. Debugowanie tych struktur wymaga głębszego zrozumienia kompozycji stanów.

1. Regiony ortogonalne

Regiony współbieżne działają niezależnie. Wada w jednym regionie może nie od razu wpłynąć na drugi, co prowadzi do niezgodnych ogólnych stanów systemu.

- Upewnij się, że zdarzenia w jednym regionie nie zmieniają niechcianie zmiennych używanych przez inny.

- Sprawdź punkty synchronizacji, w których regiony muszą być zsynchronizowane.

- Upewnij się, że stan systemu jest poprawną kombinacją stanów wszystkich regionów.

2. Zagnieżdżone stany i dziedziczenie

Zagnieżdżone stany dziedziczą zachowanie od rodzica. Jednak to dziedziczenie może ukrywać konkretne błędy logiki.

- Czy stan potomny poprawnie nadpisuje działanie wyjścia rodzica?

- Czy zdarzenia są obsługiwane na poziomie rodzica czy potomka?

- Podczas wyjścia z potomka, czy wywoływane jest działanie wyjścia rodzica?

3. Stany historii

Stany historii pozwalają stanowi złożonemu pamiętać swój ostatni stan podrzędny. Jest to często źródłem zamieszania.

- Historia głęboka: Wraca do najgłębszego aktywnego stanu podrzędnego.

- Historia powierzchniowa: Wraca do ostatniego aktywnego stanu na poziomie bezpośrednim.

- Upewnij się, że token historii jest poprawnie aktualizowany przy wejściu.

- Debuguj scenariusze, w których stan historii jest wywoływany przed pełnym zainicjowaniem stanu złożonego.

✅ Lista weryfikacji

Aby upewnić się, że maszyna stanów jest odporna, przejdź przez tę listę weryfikacji. Obejmuje ona kluczowe obszary wyznaczone w tym poradniku.

| Kategoria | Sprawdzany element | Priorytet |

|---|---|---|

| Topologia | Czy wszystkie stany są osiągalne ze stanu początkowego? | Wysoki |

| Topologia | Czy istnieją zakleszczenia (stanu bez wyjścia)? | Wysoki |

| Logika | Czy wszystkie zdarzenia mają zdefiniowany obsługę lub przejście domyślne? | Wysoki |

| Logika | Czy warunki zabezpieczające są wzajemnie wykluczające tam, gdzie to konieczne? | Średni |

| Zrównoleglenie | Czy regiony ortogonalne bezpiecznie dzielą stan zmienialny? | Średni |

| Historia | Czy stan historii został poprawnie zainicjowany przy pierwszym wejściu? | Średni |

| Testowanie | Czy każde przejście zostało wykonane w przypadku testowym? | Wysoki |

| Rejestrowanie | Czy wejście/wyjście stanu są rejestrowane do celów diagnostycznych? | Średni |

🧠 Typowe sytuacje i rozwiązania

Poniżej znajdują się konkretne sytuacje często pojawiające się podczas debugowania oraz zalecane strategie ich rozwiązywania.

Sytuacja 1: System zamarza

Jeśli aplikacja przestaje reagować, maszyna stanów prawdopodobnie znajduje się w stanie zakleszczenia. Może to się zdarzyć, gdy otrzymuje się zdarzenie, ale żadne przejście nie pasuje do tego zdarzenia w bieżącym stanie.

- Diagnoza: Sprawdź logi ostatniego wejścia do stanu.

- Rozwiązanie: Dodaj przejście domyślne lub obsługę ogólnej zdarzeń do stanu problemowego.

- Zapobieganie: Wprowadź zasade, że każdy stan musi mieć jawny „inny” przejście.

Scenariusz 2: System pomija stany

System wydaje się pomijać stan lub wchodzić w stan, w którym nie powinien. Jest to często spowodowane nieuzasadnionymi przejściami lub niepoprawną logiką warunków.

- Diagnoza: Porównaj rzeczywistą sekwencję zdarzeń z diagramem.

- Rozwiązanie: Zacieśnij warunki warunkowe lub usuń niejednoznaczne przejścia.

- Zapobieganie: Używaj jasnych zasad nazewnictwa zdarzeń, aby uniknąć kolizji.

Scenariusz 3: Niespójne przywracanie stanu

Po opuszczeniu i ponownym wejściu do stanu złożonego system nie pamięta, gdzie był. Wskazuje to na błąd w implementacji stanu historii.

- Diagnoza: Śledź ścieżkę tokenu historii.

- Rozwiązanie: Sprawdź, czy stan historii wskazuje na poprzedni aktywny stan podstawowy.

- Zapobieganie: Dokumentuj zachowanie historii jasno w fazie projektowania.

🔄 Iteracyjna poprawa

Projektowanie maszyny stanów rzadko jest doskonały w pierwszym podejściu. Debugowanie jest częścią procesu projektowania. Gdy identyfikujesz wady, dopasowujesz diagram. Ta iteracyjna pętla zapewnia, że ostateczny model jest odporny.

Gdy znajdziesz wadę, nie naprawiaj tylko kodu. Zaktualizuj diagram. Jeśli kod różni się od diagramu, diagram jest źródłem prawdy. Ta zgodność jest kluczowa dla długoterminowej utrzymywalności.

📝 Podsumowanie najlepszych praktyk

- Zachowaj prostotę: Unikaj nadmiernie skomplikowanych hierarchii, które zakrywają logikę.

- Dokumentuj warunki: W komentarzach wyjaśnij, dlaczego istnieje warunek przejścia.

- Testuj przypadki brzegowe: Skup się na granicach przestrzeni stanów.

- Wizualizuj ścieżki: Używaj narzędzi rysunkowych, aby ręcznie prześledzić ścieżki przed kodowaniem.

- Monitoruj produkcję:Skonfiguruj alerty dla anomalii stanu w środowiskach produkcyjnych.

Zastosowanie tych strategii pozwala znacznie zmniejszyć ryzyko ukrytych błędów logiki. Dobrze przetestowany maszyn stanów stanowi niezawodną podstawę dla złożonego zachowania systemu. Przekształca potencjalny chaos w przewidywalne, kontrolowane działanie.