Diseñar máquinas de estado es un ejercicio de precisión. Una transición mal colocada o un evento no definido puede desencadenar un comportamiento impredecible en el sistema. Cuando el código se ejecuta, a menudo sigue el diagrama, pero el diagrama en sí puede ocultar contradicciones. Depurar un diagrama de estado requiere un cambio de mentalidad respecto a la inspección de código típica hacia la teoría de grafos y la verificación lógica. Esta guía describe cómo identificar y resolver fallas lógicas ocultas dentro de los modelos de máquinas de estado.

Ya sea que esté trabajando con diagramas de estado UML, máquinas de estado finitas (FSM) o lógica de estado personalizada, los desafíos fundamentales permanecen consistentes. La complejidad aumenta con la jerarquía, la concurrencia y los estados de historia. Este artículo se centra en las estrategias principales para validar estos modelos antes de que lleguen a entornos de producción.

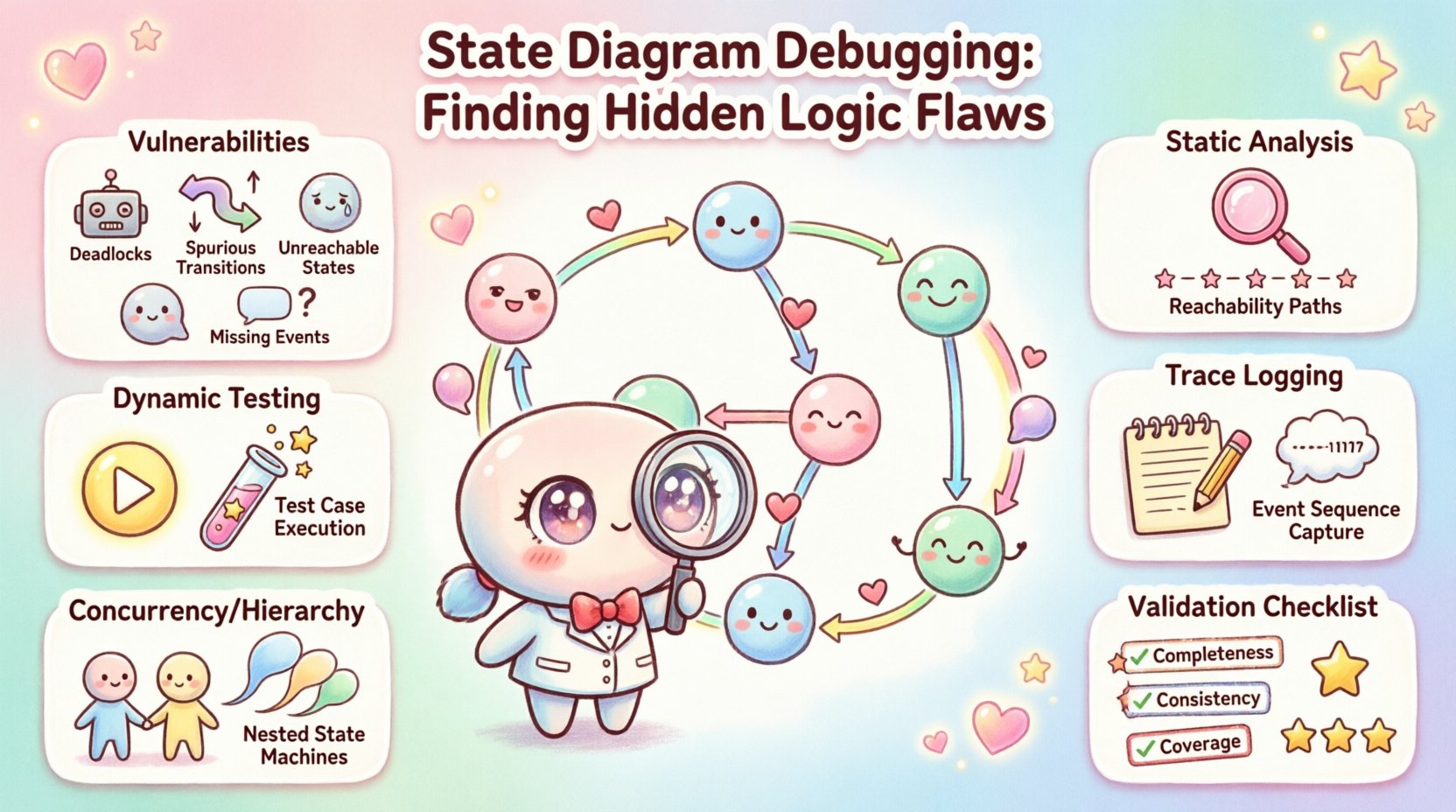

🧩 Comprender las vulnerabilidades de las máquinas de estado

Los diagramas de estado son representaciones visuales del comportamiento del sistema. Aunque ofrecen claridad, también introducen modos de fallo específicos que son distintos de los errores en código procedimental. Estas vulnerabilidades a menudo provienen de la topología del grafo, más que de la implementación de los manejadores de eventos.

Al depurar, primero debe buscar problemas de integridad estructural. Una máquina de estado que no puede alcanzar un estado terminal o se queda atrapada en un bucle sin progreso está fundamentalmente defectuosa. A continuación se presentan las principales categorías de fallas lógicas encontradas en los diagramas de estado.

- Muertes en espera: Un estado en el que no existen transiciones salientes para el evento actual, deteniendo el sistema.

- Transiciones espurias: Eventos que desencadenan caminos no deseados debido a estados objetivo ambiguos.

- Estados inalcanzables: Estados que no pueden ser alcanzados desde el estado inicial, lo que los hace inútiles.

- Estados redundantes: Varios estados que realizan funciones idénticas, complicando la mantenibilidad.

- Eventos faltantes: Escenarios en los que el sistema carece de un manejador para una entrada específica en un estado dado.

- Errores en estados de historia: Errores lógicos relacionados con estados de historia superficial o profunda que restauran un contexto incorrecto.

Identificar estos problemas temprano evita reestructuraciones costosas más adelante. El proceso de depuración implica tanto una revisión estática del modelo como una prueba dinámica de las rutas de ejecución.

🛠️ Enfoques de análisis estático

El análisis estático implica examinar el diagrama sin ejecutar la lógica subyacente. Esta fase es crucial para detectar errores de topología antes de que se genere o escriba cualquier código. El objetivo es verificar las propiedades matemáticas del grafo de estados.

1. Análisis de alcanzabilidad

Cada estado en un diagrama bien formado debería ser alcanzable desde el nodo inicial. Para depurar esto, traza una ruta desde el estado inicial hasta cada uno de los demás estados. Si un estado no puede ser alcanzado, es un artefacto de diseño que no cumple ninguna función.

- Comience en el Estado inicial.

- Siga todas las flechas de transición posibles.

- Marque cada estado visitado.

- Compare los estados marcados con el número total de estados.

- Cualquier estado no marcado es inalcanzable.

Los estados inaccesibles a menudo ocurren cuando un subestado está anidado dentro de un estado compuesto que nunca se entra. En escenarios de depuración, eliminar estos estados reduce la carga cognitiva para los futuros mantenedores.

2. Completitud de las transiciones

Cada estado debe definir un comportamiento para los eventos esperados. Si ocurre un evento en un estado donde no se define ninguna transición, el comportamiento del sistema es indefinido. Esta es una causa común de fallos en tiempo de ejecución o fallas silenciosas.

Al revisar el diagrama, busque:

- Transiciones predeterminadas:¿El estado maneja las entradas inesperadas de forma adecuada?

- Cobertura de eventos:¿Se han mapeado todas las llamadas a la API documentadas o las acciones del usuario a transiciones?

- Condiciones de guarda:¿Existen condiciones de guarda que evitan que todas las transiciones se activen simultáneamente, creando un bloqueo?

Una máquina de estados robusta maneja los escenarios de “¿y si?”. Si una condición de guarda de una transición se evalúa como falsa, ¿a dónde va el flujo? Si no hay una alternativa, el sistema se detiene.

3. Detección de ciclos

Los bucles infinitos dentro de una máquina de estados pueden consumir recursos o congelar el procesador. Aunque algunos bucles son intencionales (por ejemplo, esperar entrada), otros son accidentales.

- Rastree los caminos que regresan al mismo estado sin consumir tiempo ni eventos.

- Identifique los bucles que dependen únicamente de condiciones de guarda que nunca cambian.

- Asegúrese de que los bucles tengan un mecanismo para salir, como un tiempo de espera o una señal externa.

🧪 Pruebas dinámicas y caminos de ejecución

El análisis estático es potente, pero no puede simular el tiempo y el estado del entorno de ejecución. Las pruebas dinámicas implican alimentar eventos al sistema y observar los cambios reales de estado. Es aquí donde a menudo se revelan fallas lógicas ocultas.

1. Pruebas de cobertura de caminos

El objetivo es ejecutar cada transición posible al menos una vez. Esto requiere diseñar casos de prueba que obliguen al sistema a pasar por estados específicos.

- Asocie los casos de prueba con las transiciones en el diagrama.

- Asegúrese de probar la ruta negativa (donde no debería ocurrir una transición).

- Verifique que el sistema permanezca en el estado correcto después del evento.

- Registre el ID del estado después de cada evento para confirmar que el diagrama coincide con la realidad.

2. Pruebas de estrés en transiciones de estado

Los eventos rápidos y continuos pueden revelar condiciones de carrera. Si dos eventos llegan en rápida sucesión, ¿la máquina de estados los procesa en el orden correcto? ¿Se actualiza el estado de forma atómica?

- Envíe eventos de alta frecuencia al manejador de estados.

- Observe si el sistema omite estados o los procesa fuera de orden.

- Verifique si los estados intermedios son visibles o si el sistema salta directamente al estado final.

3. Pruebas de condiciones de borde

Los casos límite a menudo ocultan errores lógicos. ¿Qué sucede cuando una máquina de estados está en su estado final y recibe una entrada? ¿Qué sucede si se activa una transición inmediatamente después de la entrada en un estado?

- Prueba el Acción de entrada vs. el Acción de salida timing.

- Verifica el comportamiento al pasar del estado inicial directamente a un subestado complejo.

- Comprueba el comportamiento cuando se invoca un estado de historial múltiples veces.

🔎 Registro de trazas y correlación de eventos

Cuando ocurre un error en producción, el diagrama de estados es tu mapa. Para encontrar el fallo, necesitas una pista. Implementar un mecanismo de registro robusto es esencial para depurar máquinas de estados.

1. Registro de entrada y salida de estados

Cada vez que el sistema entra o sale de un estado, debe registrar este evento. Esto proporciona una cronología de la ejecución.

- Registra el Estado de origen.

- Registra el Estado objetivo.

- Registra el Evento desencadenante.

- Registra el Marca de tiempo y Datos de contexto.

Estos datos te permiten reconstruir la ruta que siguió el sistema hasta llegar al error.

2. Evaluación de condiciones de guarda

Las transiciones dependen a menudo de condiciones de guarda (condiciones booleanas). Si una transición falla, ¿fue porque la condición de guarda era falsa, o porque el evento era desconocido?

- Registra el resultado de la evaluación de cada condición de guarda.

- Registre las variables utilizadas en la condición de guarda.

- Identifique si una condición de guarda es demasiado restrictiva.

Sin esta visibilidad, es difícil distinguir entre un error lógico en la máquina de estados y un error lógico en los datos que impulsan la condición de guarda.

⚡ Manejo de concurrencia y jerarquía

Los diagramas de estados avanzados utilizan regiones ortogonales (concurrencia) y estados anidados (jerarquía). Estas características añaden poder, pero también una complejidad significativa. Depurar estas estructuras requiere una comprensión más profunda de la composición de estados.

1. Regiones ortogonales

Las regiones concurrentes se ejecutan de forma independiente. Un fallo en una región podría no afectar inmediatamente a la otra, lo que lleva a estados del sistema globales inconsistentes.

- Verifique que los eventos en una región no modifiquen inadvertidamente las variables utilizadas por otra.

- Verifique los puntos de sincronización donde las regiones deben alinearse.

- Asegúrese de que el estado del sistema sea una combinación válida de todos los estados de las regiones.

2. Estados anidados e herencia

Los estados anidados heredan el comportamiento de su padre. Sin embargo, esta herencia puede ocultar errores lógicos específicos.

- ¿El estado hijo anula correctamente la acción de salida del padre?

- ¿Los eventos se gestionan a nivel de padre o a nivel de hijo?

- ¿Cuando se sale de un estado hijo, se activa la acción de salida del padre?

3. Estados de historia

Los estados de historia permiten que un estado compuesto recuerde su último subestado. Esto suele ser una fuente de confusión.

- Historia profunda: Vuelve al subestado activo más profundo.

- Historia superficial: Vuelve al último estado activo en el nivel inmediato.

- Asegúrese de que el token de historia se actualice correctamente al entrar.

- Depure escenarios en los que se invoque el estado de historia antes de que el estado compuesto esté completamente inicializado.

✅ Lista de verificación de validación

Para asegurarse de que su máquina de estados sea robusta, recorra esta lista de verificación. Cubre las áreas críticas identificadas en esta guía.

| Categoría | Elemento de verificación | Prioridad |

|---|---|---|

| Topología | ¿Son todos los estados alcanzables desde el estado inicial? | Alto |

| Topología | ¿Hay algún bloqueo (estados sin salida)? | Alto |

| Lógica | ¿Todas las señales tienen un controlador definido o una transición predeterminada? | Alto |

| Lógica | ¿Las condiciones de guarda son mutuamente excluyentes cuando es necesario? | Medio |

| Concurrencia | ¿Las regiones ortogonales comparten de forma segura un estado mutable? | Medio |

| Historial | ¿Se inicializa correctamente el estado de historial en la primera entrada? | Medio |

| Pruebas | ¿Se ha ejecutado cada transición en una prueba? | Alto |

| Registro | ¿Se registra la entrada/salida del estado para facilitar la solución de problemas? | Medio |

🧠 Escenarios comunes y soluciones

A continuación se presentan escenarios específicos que con frecuencia se encuentran durante la depuración y las estrategias recomendadas para resolverlos.

Escenario 1: El sistema se congela

Si la aplicación deja de responder, es probable que la máquina de estados se encuentre en un estado de bloqueo. Esto ocurre cuando se recibe un evento, pero ninguna transición coincide con el evento en el estado actual.

- Diagnóstico:Revise los registros para encontrar el último estado ingresado.

- Solución:Agregue una transición predeterminada o un controlador de captura total al estado problemático.

- Prevención: Impone una regla según la cual cada estado debe tener una ruta explícita “else”.

Escenario 2: El sistema salta estados

El sistema parece omitir un estado o ingresar a un estado que no debería. Esto suele deberse a transiciones espurias o lógica de guardas incorrecta.

- Diagnóstico: Compara la secuencia real de eventos con el diagrama.

- Corrección: Ajusta las condiciones de guarda o elimina las transiciones ambiguas.

- Prevención: Usa convenciones de nombrado claras para los eventos para evitar colisiones.

Escenario 3: Restauración de estado inconsistente

Después de salir y volver a ingresar a un estado compuesto, el sistema no recuerda dónde estaba. Esto indica un error en la implementación del estado de historia.

- Diagnóstico: Rastrea la ruta del token de historia.

- Corrección: Verifica que el estado de historia apunte al subestado activo correcto.

- Prevención: Documenta claramente el comportamiento de historia en la fase de diseño.

🔄 Mejora iterativa

El diseño de máquinas de estado rara vez es perfecto en el primer intento. Depurar forma parte del proceso de diseño. A medida que identificas fallos, refinas el diagrama. Este ciclo iterativo asegura que el modelo final sea resistente.

Cuando encuentres un fallo, no solo arregles el código. Actualiza el diagrama. Si el código difiere del diagrama, el diagrama es la fuente de verdad. Esta alineación es crítica para la mantenibilidad a largo plazo.

📝 Resumen de mejores prácticas

- Manténlo simple: Evita jerarquías excesivamente complejas que oculten la lógica.

- Documenta las guardas: Explica por qué existe una condición de transición en los comentarios.

- Prueba casos límite: Enfócate en los límites de tu espacio de estados.

- Visualiza caminos: Usa herramientas de dibujo para trazar caminos manualmente antes de codificar.

- Monitoreo de Producción:Configura alertas para anomalías de estado en entornos en vivo.

Al aplicar estas estrategias, puedes reducir significativamente el riesgo de fallas lógicas ocultas. Una máquina de estados bien depurada es una base confiable para el comportamiento de sistemas complejos. Transforma el caos potencial en una ejecución predecible y controlada.